# 学位申請論文

セル電圧均等化回路の有用性向上に関する研究

2019年3月

佐藤 大記

# 目次

| 第1章  | 亨論                          | 1  |

|------|-----------------------------|----|

| 1.1  | セル電圧均等化回路の必要性               | 2  |

| 1.2  | 従来回路における課題                  | 4  |

| 1.3  | 本論文の目的と意義                   | 6  |

| 1.4  | 本論文の構成                      | 7  |

| 第2章] | LC 直列回路方式セル電圧均等化回路の提案       | 9  |

| 2.1  | 提案回路の構成と特徴                  | 9  |

|      | 2.1.1 動作モード                 | 11 |

|      | 2.1.2 提案回路の特徴               | 14 |

|      | 2.1.3 動作原理                  | 16 |

| 2.2  | 各回路パラメータの設計法                | 19 |

|      | 2.2.1 回路素子 L, C の設計指針       | 19 |

|      | 2.2.2 セル切替周期 $T_{CC}$ の設計指針 | 21 |

| 2.3  | シミュレーションによる動作特性の検証          | 36 |

| 2.4  | 実機実験による動作特性の検証              | 45 |

| 2.5  | 提案回路の課題                     | 56 |

| 2.6  | 第2章のまとめ                     | 58 |

| 第3章: | 擬似乱数列を用いた均等化時間低減法           | 59 |

| 3.1  | 提案制御手法の概要と目的                | 59 |

| 3.2  | 動作原理                        | 60 |

| 3.3  | シミュレーションによる有用性の検証           | 62 |

|      | 3.3.1 従来制御法と疑似乱数法の比較        | 64 |

| 3.4  | 実機実験による有用性の検証               | 67 |

|      | 3.4.1 従来制御法と疑似乱数法の比較        | 71 |

| 3.5  | 平均均等化時間についての考察              | 73 |

| 3.6                                                           | 均等化時間のばらつきについての考察                                                                                                     | 73                                                          |

|---------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------|

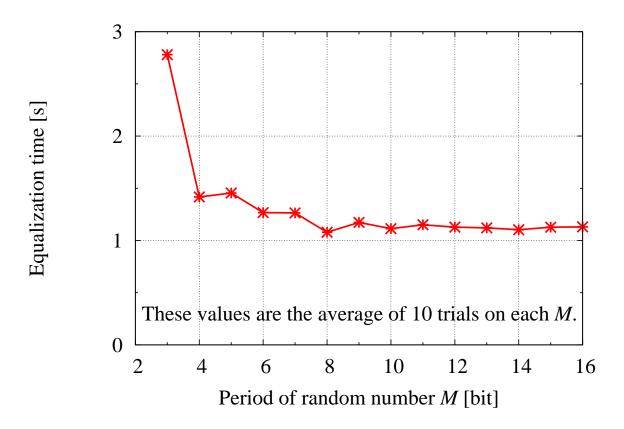

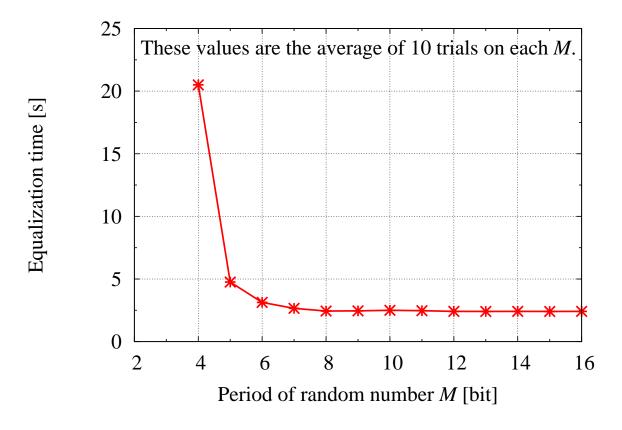

| 3.7                                                           | 乱数周期 M が均等化時間に与える影響                                                                                                   | 74                                                          |

| 3.8                                                           | 第3章のまとめ                                                                                                               | 76                                                          |

| 第4章                                                           | 蓄電セル電圧の大小関係推定を利用した均等化時間低減法                                                                                            | 77                                                          |

| 4.1                                                           | 提案制御手法の概要と目的                                                                                                          | 77                                                          |

| 4.2                                                           | 動作原理                                                                                                                  | 80                                                          |

|                                                               | 4.2.1 各セル電圧大小関係の推定方法                                                                                                  | 80                                                          |

|                                                               | 4.2.2 推定した大小関係を利用したセルの選択                                                                                              | 82                                                          |

|                                                               | 4.2.3 選択したセル間の電圧差の収束判定                                                                                                | 83                                                          |

| 4.3                                                           | 最大電圧セルと最小電圧セル間の電圧差検出方法                                                                                                | 86                                                          |

| 4.4                                                           | シミュレーションによる有用性の検証                                                                                                     | 90                                                          |

|                                                               | 4.4.1 従来制御法と大小関係推定法の比較                                                                                                | 92                                                          |

| 4.5                                                           | 実機実験による有用性の検証                                                                                                         | 94                                                          |

|                                                               | 4.5.1 従来制御法と大小関係推定法の比較                                                                                                | 96                                                          |

| 4.6                                                           | 第4章のまとめ                                                                                                               | 98                                                          |

|                                                               |                                                                                                                       |                                                             |

| 第5章                                                           | 回生型ゲート駆動回路を用いたゲート駆動回路の簡素化                                                                                             | 99                                                          |

| 第 <b>5</b> 章  <br>5.1                                         | 回生型ゲート駆動回路を用いたゲート駆動回路の簡素化<br>回生型ゲート駆動回路を提案回路に適用した際の回路構成                                                               | <b>99</b><br>101                                            |

|                                                               |                                                                                                                       |                                                             |

| 5.1                                                           | 回生型ゲート駆動回路を提案回路に適用した際の回路構成                                                                                            | 101                                                         |

| 5.1<br>5.2                                                    | 回生型ゲート駆動回路を提案回路に適用した際の回路構成                                                                                            | 101<br>104<br>105                                           |

| 5.1<br>5.2<br>5.3                                             | 回生型ゲート駆動回路を提案回路に適用した際の回路構成                                                                                            | 101<br>104<br>105<br>107                                    |

| 5.1<br>5.2<br>5.3<br>5.4                                      | 回生型ゲート駆動回路を提案回路に適用した際の回路構成                                                                                            | 101<br>104<br>105<br>107                                    |

| 5.1<br>5.2<br>5.3<br>5.4<br>5.5                               | 回生型ゲート駆動回路を提案回路に適用した際の回路構成                                                                                            | 101<br>104<br>105<br>107<br>111                             |

| 5.1<br>5.2<br>5.3<br>5.4<br>5.5<br>5.6                        | 回生型ゲート駆動回路を提案回路に適用した際の回路構成                                                                                            | 101<br>104<br>105<br>107<br>111<br>114                      |

| 5.1<br>5.2<br>5.3<br>5.4<br>5.5<br>5.6<br>5.7                 | 回生型ゲート駆動回路を提案回路に適用した際の回路構成                                                                                            | 101<br>104<br>105<br>107<br>111<br>114<br>120               |

| 5.1<br>5.2<br>5.3<br>5.4<br>5.5<br>5.6<br>5.7                 | 回生型ゲート駆動回路を提案回路に適用した際の回路構成 回生型ゲート駆動回路の制御法 3巻線トランスの設計指針 シミュレーションによる動作特性の検証 実機実験による動作特性の検証 バッテリモジュール充電時の動作特性 第5章のまとめ 結論 | 101<br>104<br>105<br>107<br>111<br>114<br>120<br><b>121</b> |

| 5.1<br>5.2<br>5.3<br>5.4<br>5.5<br>5.6<br>5.7<br>第 <b>6</b> 章 | 回生型ゲート駆動回路を提案回路に適用した際の回路構成 回生型ゲート駆動回路の制御法 3巻線トランスの設計指針 シミュレーションによる動作特性の検証 実機実験による動作特性の検証 バッテリモジュール充電時の動作特性 第5章のまとめ 結論 | 101<br>104<br>105<br>107<br>111<br>114<br>120<br>121        |

# 図目次

| 1.1  | Conceptual diagram of a smart community                                                          | 1  |

|------|--------------------------------------------------------------------------------------------------|----|

| 1.2  | Comparison of the available voltage ranges between balanced and imbalanced modules.              | 3  |

| 1.3  | Conventional cell voltage equalizers                                                             | 5  |

| 2.1  | LC series circuit type cell voltage equalizer                                                    | 10 |

| 2.2  | Operating modes of the proposed voltage equalizer connected to three series-connected            |    |

|      | cells                                                                                            | 12 |

| 2.3  | Comparison between operating modes and simulation current waveforms                              | 13 |

| 2.4  | Equivalent circuit of a part of the proposed cell voltage equalizer                              | 17 |

| 2.5  | Simulation results of the relationship between the cell change cycle $T_{\rm CC}$ and the equal- |    |

|      | ization time under three cells condition                                                         | 23 |

| 2.6  | Simulation results of the relationship between the cell change cycle $T_{\rm CC}$ and the equal- |    |

|      | ization time under eight cells condition                                                         | 23 |

| 2.7  | Simulation results of the relationship between the cell change cycle $T_{\rm CC}$ and the equal- |    |

|      | ization time under sixteen cells condition                                                       | 24 |

| 2.8  | Comparison among the simulation results of the relationships on the number of cells $n$ .        | 24 |

| 2.9  | Simulation results of the relationship between the cell change cycle $T_{\rm CC}$ and the time   |    |

|      | constant of the LC series circuit                                                                | 27 |

| 2.10 | Comparison among the relationships between the cell change cycle $T_{\rm CC}$ and the tran-      |    |

|      | sient response characteristics of the LC series circuit                                          | 29 |

| 2.11 | Comparison among the relationships between the cell change cycle $T_{\rm CC}$ and the dead-      |    |

|      | time $T_{\text{dead}}$                                                                           | 31 |

| 2.12 | Comparison among the relationships between the current limit value $i_{ref}$ and the equal-      |    |

|      | ization time                                                                                     | 33 |

| 2.13 | Experimental results of the relationships between the equalization time and the cell             |    |

|      | change cycle $T_{\text{CC}}$                                                                     | 35 |

| 2.14 | Experimental results of the relationships between the efficiency and the cell change     |    |

|------|------------------------------------------------------------------------------------------|----|

|      | cycle $T_{\rm CC}$                                                                       | 35 |

| 2.15 | Simulation current waveforms of each cell of three series-connected cells                | 39 |

| 2.16 | Simulation current waveforms of each cell of eight series-connected cells                | 40 |

| 2.17 | Simulation current waveforms of each cell of sixteen series-connected cells              | 40 |

| 2.18 | Simulation results of the proposed cell voltage equalizer connected to three series-     |    |

|      | connected cells                                                                          | 42 |

| 2.19 | Simulation results of the proposed cell voltage equalizer connected to eight series-     |    |

|      | connected cells                                                                          | 43 |

| 2.20 | Simulation results of the proposed cell voltage equalizer connected to sixteen series-   |    |

|      | connected cells                                                                          | 44 |

| 2.21 | Experimental results of the proposed cell voltage equalizer connected to three series-   |    |

|      | connected EDLC cells                                                                     | 50 |

| 2.22 | Experimental results of the proposed cell voltage equalizer connected to eight series-   |    |

|      | connected EDLC cells                                                                     | 51 |

| 2.23 | Comparison of the experimental and simulation current waveforms of each cell $(n = 3)$ . | 52 |

| 2.24 | Comparison of the experimental and simulation current waveforms of each cell $(n = 8)$ . | 53 |

| 2.25 | Experimental results of the proposed cell voltage equalizer connected to eight series-   |    |

|      | connected lithium-ion battery cells                                                      | 55 |

| 2.26 | Simulation results with the conventional method                                          | 57 |

| 3.1  | Flowchart of the proposed equalization time reduction method using pseudo-random         |    |

|      | numbers                                                                                  | 61 |

| 3.2  | Simulation results with the proposed reduction method using pseudo-random numbers.       | 63 |

| 3.3  | Simulation results with conventional method (represented below as Fig. 2.26)             | 65 |

| 3.4  | Equalization time comparison between the proposed reduction method and the con-          |    |

|      | ventional method in the simulation                                                       | 66 |

| 3.5  | Experimental results with the conventional method                                        | 68 |

| 3.6  | Experimental results with the proposed reduction method using pseudo-random num-         |    |

|      | bers                                                                                     | 70 |

| 3.7  | Equalization time comparison between the proposed reduction method and the con-          |    |

|      | ventional method in the experiment                                                       | 72 |

| 3.8  | Characteristics of the equalization time to the period of random number M under eight                   |     |

|------|---------------------------------------------------------------------------------------------------------|-----|

|      | cells condition.                                                                                        | 75  |

| 3.9  | Characteristics of the equalization time to the period of random number $M$ under                       |     |

|      | sixteen cells condition                                                                                 | 75  |

| 4.1  | Flowchart of the proposed equalization time reduction method using a cell voltage                       |     |

|      | estimation                                                                                              | 79  |

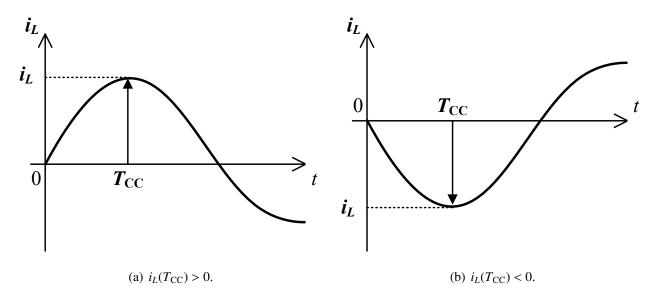

| 4.2  | Detection of the equalization current direction                                                         | 81  |

| 4.3  | Conceptual diagram of the cell voltage estimate                                                         | 81  |

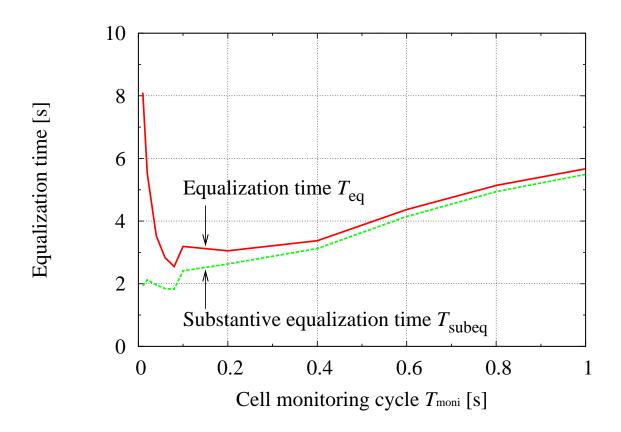

| 4.4  | Characteristics between the equalization time $T_{\rm eq}$ and the cell monitoring cycle $T_{\rm moni}$ |     |

|      | in the simulation.                                                                                      | 85  |

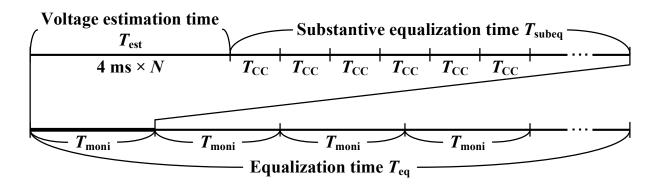

| 4.5  | Relationship among the substantive equalization time $T_{\text{subeq}}$ , the voltage estimation        |     |

|      | time $T_{\rm est}$ , the equalization time $T_{\rm eq}$ and the cell monitoring cycle $T_{\rm moni}$    | 85  |

| 4.6  | Equivalent circuit of the proposed cell voltage equalizer $(N = 2)$                                     | 89  |

| 4.7  | Conceptual diagram of the input voltage on the LC series circuit and the equalization                   |     |

|      | current waveforms.                                                                                      | 89  |

| 4.8  | Simulation results with the proposed reduction method using a cell voltage estimation.                  | 91  |

| 4.9  | Simulation results with the conventional method                                                         | 93  |

| 4.10 | Experimental results with the proposed reduction method using a cell voltage estimation.                | 95  |

| 4.11 | Experimental results with the conventional method                                                       | 97  |

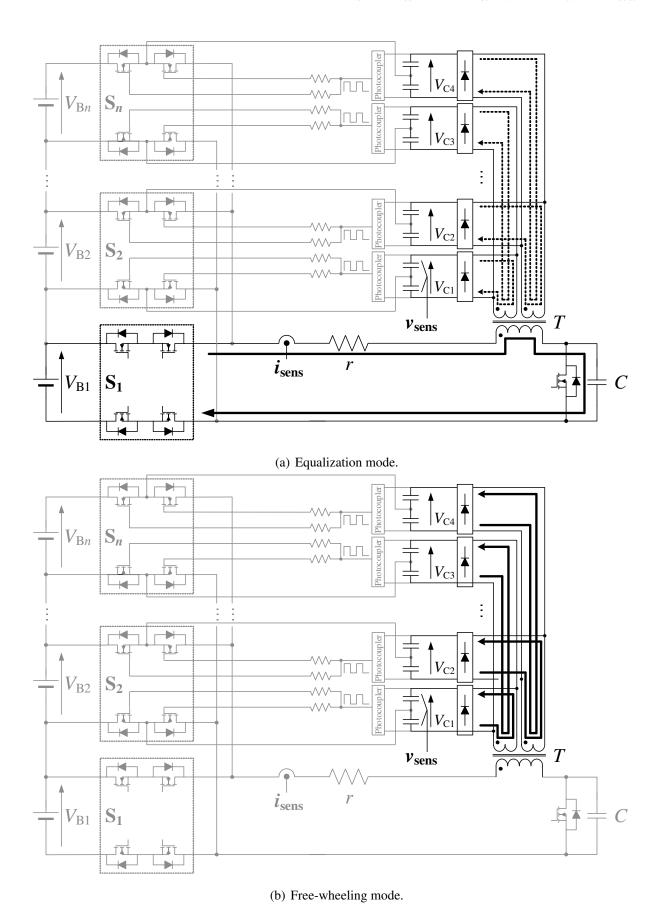

| 5.1  | Appearance of the proposed cell voltage equalizer using Photo-MOS Relays                                | 100 |

| 5.2  | Circuit configuration of the proposed cell voltage equalizer with a regenerative gate                   |     |

|      | drive circuit                                                                                           | 102 |

| 5.3  | Operation modes of the proposed regenerative gate drive circuit                                         | 103 |

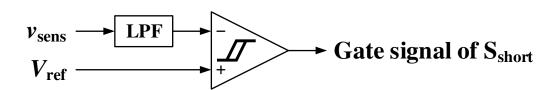

| 5.4  | Block diagram of the control method for the proposed regenerative gate drive circuit.                   | 104 |

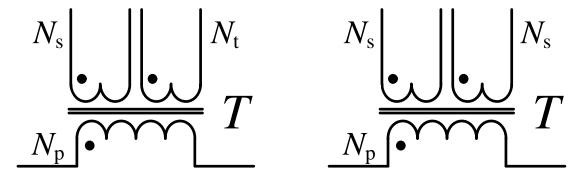

| 5.5  | Conceptual diagrams of three-winding transformers                                                       | 105 |

| 5.6  | Simulation results of the proposed regenerative gate drive circuit                                      | 109 |

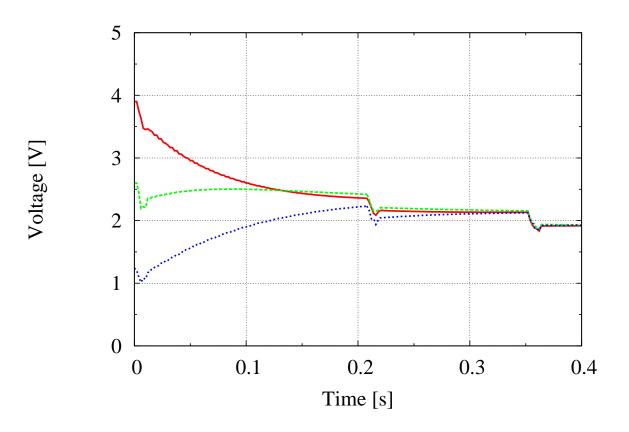

| 5.7  | Voltages of each gate drive capacitor $V_{\text{C1-C4}}$                                                | 110 |

| 5.8  | Experimental results of the proposed regenerative gate drive circuit                                    | 113 |

| 5.9  | Connection diagram of a battery module with an external power supply                                    | 116 |

| 5.10 | Experimental results of the proposed regenerative gate drive circuit (in charging state).               | 117 |

| 5.11 | Voltage of the gate drive capacitor $V_{C1}$ (under CC charging period, $t = 5$ min)                    | 119 |

5.12 Voltage of the gate drive capacitor  $V_{C1}$  (under CV charging period, t = 15 min). . . . 119

# 表目次

| 1.1  | Comparison of the characteristics between each cell voltage equalizer                           | 5  |

|------|-------------------------------------------------------------------------------------------------|----|

| 2.1  | Comparison of the characteristics between conventional equalizers and the proposed              |    |

|      | equalizer                                                                                       | 15 |

| 2.2  | Relationships among condition of $r$ , angular frequency of the oscillation and $t_{iMax}$      | 18 |

| 2.3  | Required specifications of the simulation circuit                                               | 20 |

| 2.4  | Circuit parameters in the simulations to derive the cell change cycle $T_{\rm CC}$              | 22 |

| 2.5  | Circuit parameters in the simulations to derive the cell change cycle $T_{\rm CC}$ considering  |    |

|      | the time constant of the LC series circuit                                                      | 26 |

| 2.6  | Circuit parameters in the simulations to derive the cell change cycle $T_{\rm CC}$ considering  |    |

|      | the transient response characteristics of the LC series circuit                                 | 28 |

| 2.7  | Circuit parameters in the simulations to derive the cell change cycle $T_{\rm CC}$ inserted the |    |

|      | dead-time $T_{ m dead}$                                                                         | 30 |

| 2.8  | Circuit parameters in the simulations to derive the cell change cycle $T_{\rm CC}$ considering  |    |

|      | the current limit value $i_{\mathrm{ref}}$                                                      | 32 |

| 2.9  | Circuit parameters in the simulation for the three series-connected cells                       | 37 |

| 2.10 | Circuit parameters in the simulation for the eight series-connected cells                       | 37 |

| 2.11 | Circuit parameters in the simulation for the sixteen series-connected cells                     | 38 |

| 2.12 | Circuit parameters in the experiment for the three series-connected EDLC cells                  | 46 |

| 2.13 | Circuit parameters in the experiment for the eight series-connected EDLC cells                  | 46 |

| 2.14 | Circuit parameters in the experiment for the eight series-connected lithium-ion battery         |    |

|      | cells                                                                                           | 47 |

| 3.1  | Circuit parameters in the simulation for the proposed reduction method using pseudo-            |    |

|      | random numbers                                                                                  | 62 |

| 3.2  | Circuit parameters in the experiment for the proposed reduction method using pseudo-            |    |

|      | random numbers                                                                                  | 67 |

# 表目次

| 4.1 | Circuit parameters in the simulation for the proposed reduction method using a cell    |     |

|-----|----------------------------------------------------------------------------------------|-----|

|     | voltage estimation                                                                     | 90  |

| 4.2 | Circuit parameters in the experiment for the proposed reduction method using a cell    |     |

|     | voltage estimation.                                                                    | 94  |

| 5.1 | Parameter comparison between Photo-MOS Relays "TLP3100" and Photocouplers              |     |

|     | "TLP250H"                                                                              | 100 |

| 5.2 | Circuit parameters in the simulation for the proposed regenerative gate drive circuit  | 107 |

| 5.3 | Parameters of MOS-FETs using in the simulation                                         | 108 |

| 5.4 | Circuit parameters in the experiment for the proposed regenerative gate drive circuit. | 112 |

| 5.5 | Circuit parameters in the experiment for the proposed regenerative gate drive circuit  |     |

|     | (in charging state)                                                                    | 115 |

# 第1章 序論

近年、地球環境問題や化石燃料の枯渇問題などを背景として、Fig. 1.1 に示すようなスマートコミュニティと呼ばれる構想が広がりをみせている。スマートコミュニティとは、風力発電や太陽光発電などの自然エネルギーによる発電と、電気自動車や電気鉄道、スマートハウスといった負荷を連携させることにより、コミュニティ全体として電力を賢く利用しようという考えである[1]。しかしながら、風力発電や太陽光発電といった自然エネルギーによる発電は、日照時間や気温、風速といった気象条件によって大きく発電電力が変化するという特徴があり[2]、また、電気自動車の急速充電や電気鉄道といった負荷は、使用時と待機時で大きく消費電力が変動するため、これらの機器が増加すると系統の電力が不安定になる危険性がある[3]。そのため、電力貯蔵や電力調整を目的とした、蓄電装置の需要が高まっている。

Fig. 1.1. Conceptual diagram of the smart community [1, 2].

## 1.1 セル電圧均等化回路の必要性

蓄電装置には寿命や電力密度,エネルギー密度などの観点から電気二重層キャパシタ (EDLC: Electric Double-Layer Capacitor) やリチウムイオンバッテリが広く用いられている。しかしながら,EDLC やリチウムイオンバッテリは単セルあたりの電圧が低いため、実際に蓄電装置で用いる場合には、単セルを直列接続させたモジュールとして用いる場合が多い。このような使用では、セルごとの容量、自己放電率、内部インピーダンス、温度等の個体差により、EDLC やリチウムイオンバッテリの各セル間において電圧のばらつきが生じる [4]。なお、現状の系統電力用電力貯蔵装置としてはナトリウム硫黄電池 (NAS 電池) やレドックスフロー電池などが一般に用いられているが [5–8]、近年、電気自動車で使用されたリチウムイオンバッテリ等を系統電力用の電力貯蔵装置にて再利用する取り組みが加速していることから [9]、本論文では EDLC ならびにリチウムイオンバッテリを対象とした。

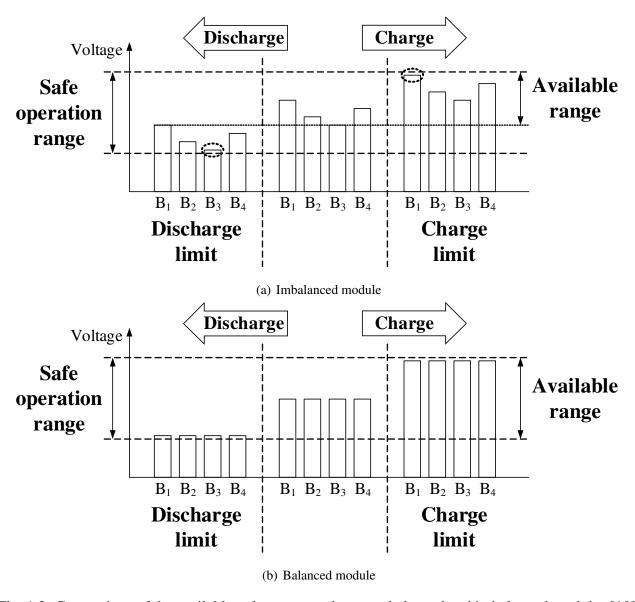

Fig. 1.2 に、各セル電圧のばらつきによるバッテリモジュール容量低下のイメージ図を示す [10]。 Fig. 1.2 では、バッテリセル  $B_{1-4}$  を直列接続したバッテリモジュールを充放電可能な状態 (図中、中央の状態) から、放電下限値 (Discharge limit) まで放電、または充電上限値 (Charge limit) まで充電した際の、各セルの電圧値とモジュール全体として利用可能な電気エネルギー量 (Available range) の関係を示している。図中の "Safe operation range" は、バッテリセルとして安全に利用可能な電圧の範囲を表しており、横軸はバッテリモジュールの充電状態を 3 段階で示し、縦軸は各セルの電圧値を表している。ここで、直列に接続したバッテリセル  $B_{1-4}$  を充放電する場合、モジュール全体として充電可能な電気エネルギーは、電圧の最も高いセルによって制限される (図中、Charge limit の点線で丸を付けたセル電圧により制限される)。 同様に、モジュール全体として放電可能な電気エネルギーは、電圧の最も低いセルによって制限される (図中、Discharge limit の点線で丸を付けたセル電圧により制限される)。 その結果、セルの電圧バランスが崩れた状態で使用可能なモジュール全体の電気エネルギー量 (Available range) は、セルの電圧バランスが整っている状態と比較して減少する。これは Fig. 1.2(a) と Fig. 1.2(b) の "Available range" の差からも明らかである。

また、EDLCやリチウムイオンバッテリは充放電の繰り返しにより劣化し、内部インピーダンスが増加する。一般的に、セルの劣化は電圧の高い状態で進行しやすいため、電圧の高いセルと低いセルの間では劣化の速度が異なり、劣化は不均一に進行する。これにより、充電時においては劣化の進行した内部インピーダンスの高いセルの電圧が高くなり、他のセルよりも更に劣化が進行する。その結果、バッテリモジュールの充放電によって得られる電気エネルギーは更に減少することとなり、セル電圧のばらつきもより一層加速する。

このように、充放電サイクルの過程で一旦セル間の電圧バランスが崩れると、セルの劣化が加速度的に進行する。更に、充放電を頻繁に繰り返すような用途においては、この劣化の速度はより高いものとなる。このような悪循環を防止し、EDLCならびにリチウムイオンバッテリの蓄電エネルギー、および充放電容量を最大限に活用するためには、セル電圧の均等化回路が必要不可欠となる[11]。

Fig. 1.2. Comparison of the available voltage ranges between balanced and imbalanced modules [10].

## 1.2 従来回路における課題

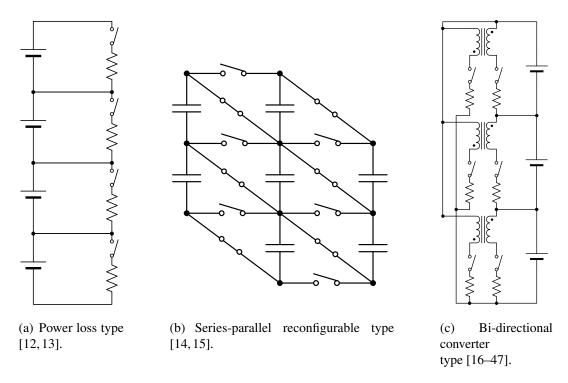

セル間の電圧のばらつきを解消するセル電圧均等化回路としては,既に様々な方式が提案されており [12-47],各方式の有用性がこれまでに比較検討されてきた(本論文ではこれらの回路をまとめて従来回路と呼ぶ)。

Fig. 1.3(a) に示す回路はセル間の電圧の均等化を図るために余剰エネルギーを抵抗で消費さ せるパッシブ型と呼ばれる方式 [12,13] であり、セル電圧均等化回路として現在最も一般に普 及している方式である[11]。パッシブ型は抵抗とスイッチング素子のみで構成されることから 構成が簡素であるという特徴を有する反面、均等化動作時の損失が必然的に大きくなるという 課題がある。また、電圧の高いセルから低いセルへ蓄電エネルギーを移すことで均等化を図る アクティブ型と呼ばれる方式 [14-47] であっても, Fig. 1.3(b) に示すようなバッテリモジュール 内のセル同士の直並列を切り替える方式 [14,15] では、均等化動作時に各セルに流れる電流(以 下,本論文では均等化電流と呼ぶ) を動的に制御できないといった課題や,Fig. 1.3(c) に示すよ うなトランス等の磁性素子やキャパシタ等の蓄電素子を用いて各セル間でコンバータを形成す ることにより各セル間で双方向に電荷の授受を行う方式 [16-47] では、一時的にエネルギー蓄 えるためのインダクタやトランス、キャパシタといった受動素子がセル数に比例して多数必要 となることから、回路規模が増大するといった課題があった。したがって、従来回路の特徴を まとめると Table 1.1 のようになり、新たなセル電圧均等化回路にはアクティブ型の採用による 均等化動作の効率向上,均等化電流の動的な制御性,およびインダクタやキャパシタといった 一時的なエネルギー貯蔵のために必要な受動素子数の削減による回路規模の低減の全ての課題 を克服することが期待される。

Fig. 1.3. Conventional cell voltage equalizers [12–47].

Table 1.1. Comparison of the characteristics between each cell voltage equalizer [12–47].

| Equalizer type                               | Efficiency       | Current controllability | Size                     |

|----------------------------------------------|------------------|-------------------------|--------------------------|

| Power loss type [12, 13]                     | × (Passive type) | Possible                | 0                        |

| Series-parallel reconfigurable type [14, 15] | ○ (Active type)  | Impossible              | 2( <i>n</i> - 1)         |

| Bi-directional converter type [16–47]        | ○ (Active type)  | Possible                | <i>n</i> or <i>n</i> - 1 |

| Expectation for a novel proposed equalizer   | ○ (Active type)  | Possible                | < n                      |

## 1.3 本論文の目的と意義

本論文では、蓄電装置の需要拡大に伴って必要性が増しているセル電圧均等化回路の更なる 有用性向上を目的とし,Table 1.1 に示したような従来回路が抱える課題に着目した新たなセル 電圧均等化回路として,LC 直列回路方式セル電圧均等化回路(以下,本論文では提案回路と呼 ぶ)を提案する。提案回路では、アクティブ方式の採用による均等化動作の効率向上と均等化電 流の動的な制御性、ならびに受動素子数の削減による回路規模の低減が期待される。また、シ ミュレーションおよび実機実験により動作特性を検証し,提案回路の有用性について検討する。 加えて、提案回路の価値の更なる向上を目的として、均等化に要する時間(以下、本論文では 均等化時間と呼ぶ) を低減する制御法(以下,本論文では均等化時間低減法と呼ぶ),および高い 制御性を維持しつつゲート駆動回路を簡素化することが可能な双方向スイッチの構成方法につ いても検討する。均等化時間低減法では、擬似乱数列を利用してセルの切替順をランダムとす る方法と、均等化動作時に流れる電流から各セル電圧の大小関係を推定することにより、バッ テリモジュール内で電圧が最も高いセルと最も低いセルとの間で選択的に均等化動作を行う方 法について提案する。これらの均等化時間低減法は、どちらも新たにセンサ等を追加する必要 がなく、制御法の変更のみで均等化時間を低減可能である。双方向スイッチの構成方法では、 ゲート駆動回路用コンバータの削減に着目した回生型ゲート駆動回路を提案する。回生型ゲー ト駆動回路の適用により、バッテリモジュールのセル数が増加した場合においても必要となる ゲート駆動回路用コンバータは3つのみとなり、ゲート駆動回路の簡素化が期待される。以上 の3つの手法それぞれについて、提案回路に適用した場合の動作特性をシミュレーションおよ び実機実験により検証し、提案手法の有用性を検討する。

これらの成果により、本論文はセル電圧均等化回路の有用性向上に寄与する。その結果、高 効率かつシンプルなセル電圧均等化回路をより手軽に蓄電装置に導入可能となる。これにより、 蓄電装置の相対的なコスト低減からスマートグリッドなどに代表される賢い電力利用が安価に 実現可能となることで、ひいては世界的なエネルギー問題への貢献が期待される。

## 1.4 本論文の構成

以下に、各章の概要を述べる。本論文は6章から構成される。

第1章では、蓄電装置の需要の高まりから、セル電圧均等化回路が今後益々必要とされる背景について述べるとともに、従来回路の特徴と課題について示し、本論文における研究の目的と意義を明確化する。

第2章では、第1章にて示した従来回路が抱える課題に対して、アクティブ方式の採用による蓄電エネルギーの有効活用、均等化電流の動的な制御性、ならびに一時的なエネルギー貯蔵のために必要な受動素子数の削減に着目した新たなセル電圧均等化回路として、LC直列回路方式セル電圧均等化回路を提案する。更に、シミュレーションと実機実験により均等化動作特性の検証を行い、セル電圧均等化回路としての提案回路の有用性を示す。加えて実機実験の結果から、提案回路は従来のパッシブ型のセル電圧均等化回路と比較して、均等化動作の効率を向上可能であることを示す。最後に、提案回路の更なる価値向上を目的として、均等化時間と双方向スイッチの構成という提案回路特有の課題についても合わせて整理する。

第3章では、第2章にて示した提案回路が抱える課題の1つである均等化時間に対して、擬似乱数列を利用してセルの切替順をランダムとすることで各バッテリセルの初期条件による影響を小さくし、均等化時間を低減可能な制御法(以下、疑似乱数法)を提案する。疑似乱数法は追加センサを必要とせず、制御法の変更のみで均等化時間を低減可能である。更に、シミュレーションと実機実験により均等化動作特性の検証を行い、疑似乱数法の有用性について検討する。加えてシミュレーションおよび実機実験の結果から、疑似乱数法は従来の制御法と比較して均等化時間を概ね低減可能であること、また各バッテリセルの初期条件に依存することなく、平均的な均等化時間を低減可能であることを示す。

第4章では、第2章にて示した提案回路が抱える課題の1つである均等化時間に対して、均等化動作時に流れる電流の向きから各バッテリセル電圧の大小関係を推定し、バッテリモジュール内で電圧が最も高いセルと最も低いセルとの間で選択的に均等化動作を行うことで均等化時間を低減可能な制御法(以下、大小関係推定法)を提案する。大小関係推定法では従来の制御法で均等化電流の制限のために使用していた電流センサを用いるため、追加センサを必要とせず、制御法の変更のみで均等化時間を低減可能である。更に、シミュレーションおよび実機実験により均等化動作特性の検証を行い、大小関係推定法の有用性について検討する。加えてシミュレーションおよび実機実験の結果から、大小関係推定法は従来の制御法と比較して均等化時間を低減可能であること,また各バッテリセル電圧のばらつき状況に合わせた均等化動作が可能であることを示す。

#### 第1章 序論

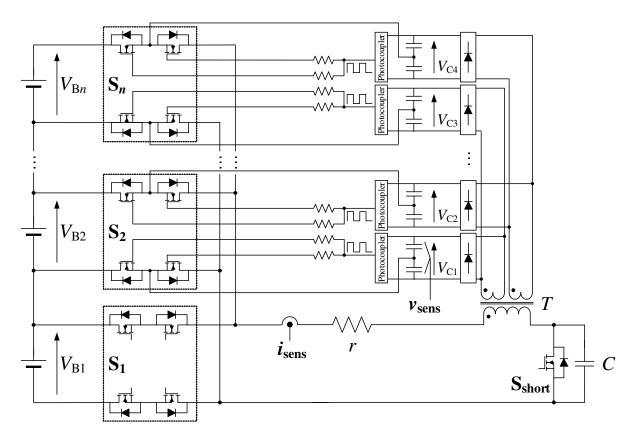

第5章では、第2章にて示した提案回路が抱える課題の1つである双方向スイッチの構成に対して、2つのnチャネル MOS-FET(Metal-Oxide-Semiconductor Field-Effect Transistor)を逆直列に接続した構成とすることで高い制御性を有するとともに、それらのゲート駆動回路用コンバータ数を削減可能な回生型ゲート駆動回路およびその制御法を提案する。更に、シミュレーションおよび実機実験により均等化動作特性ならびにゲート駆動回路用電源の生成動作特性の検証を行い、回生型ゲート駆動回路の有用性について検討する。加えてシミュレーションおよび実機実験の結果から、回生型ゲート駆動回路を用いることでバッテリモジュールのセル数が増加した場合においても3つのコンバータのみで提案回路のゲート駆動回路を構成することが可能であること、バッテリモジュールが外部電源により充電されている場合においては安定的な均等化動作ならびにゲート駆動回路用電源の生成動作が可能であることを示す。

第6章では、第2章から第5章で得られた結論を総括するとともに、今後の展望について述べる。

# 第2章 LC直列回路方式セル電圧均等化回路の提案

第2章では,第1章にて示した従来回路が抱える課題に対して,アクティブ方式の採用による蓄電エネルギーの有効活用,均等化電流の動的な制御性,ならびに一時的なエネルギー貯蔵のために必要な受動素子数の削減に着目した新たなセル電圧均等化回路として,LC直列回路方式セル電圧均等化回路を提案する。加えて,シミュレーションと実機実験により動作特性の検証を行い,セル電圧均等化回路としての提案回路の有用性について検証する。最後に,提案回路の更なる価値向上を目的として,均等化時間と双方向スイッチの構成という提案回路特有の課題についても合わせて整理する。

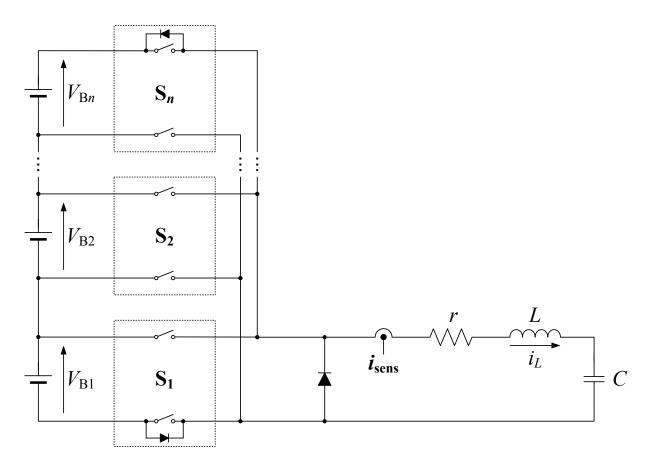

# 2.1 提案回路の構成と特徴

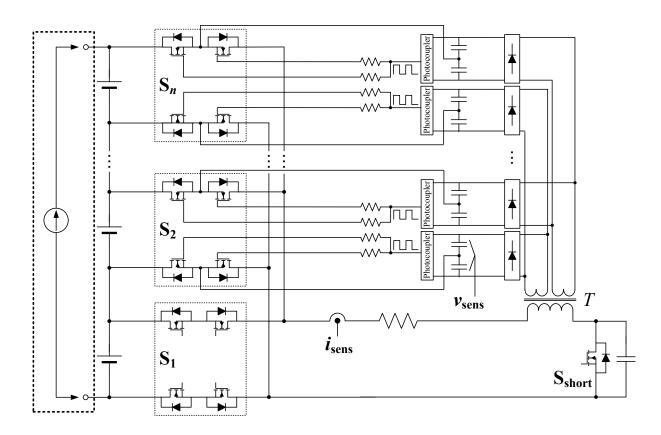

Fig. 2.1 に本章で提案する LC 直列回路方式セル電圧均等化回路を示す。提案回路は,直列に接続されたバッテリセルに対して各セルの正極と負極それぞれにスイッチング素子を接続し,スイッチング素子を用いて各セルと LC 直列回路部の接続を順次切り替えることにより,各セルの電荷をキャパシタ C を経由させて他セルに分配することで,各セル電圧の均等化を図る方式である。

図中のrは、インダクタL、およびキャパシタCの抵抗分を示している。また、任意のバッテリセル  $\mathbf{B}_j$  (j=1–n) と、 $\mathbf{LC}$  直列回路を接続するために使用する複数のスイッチング素子を、まとめて  $\mathbf{S}_i$  と表記する (図中破線部)。

Fig. 2.1. LC series circuit type cell voltage equalizer.

#### 2.1.1 動作モード

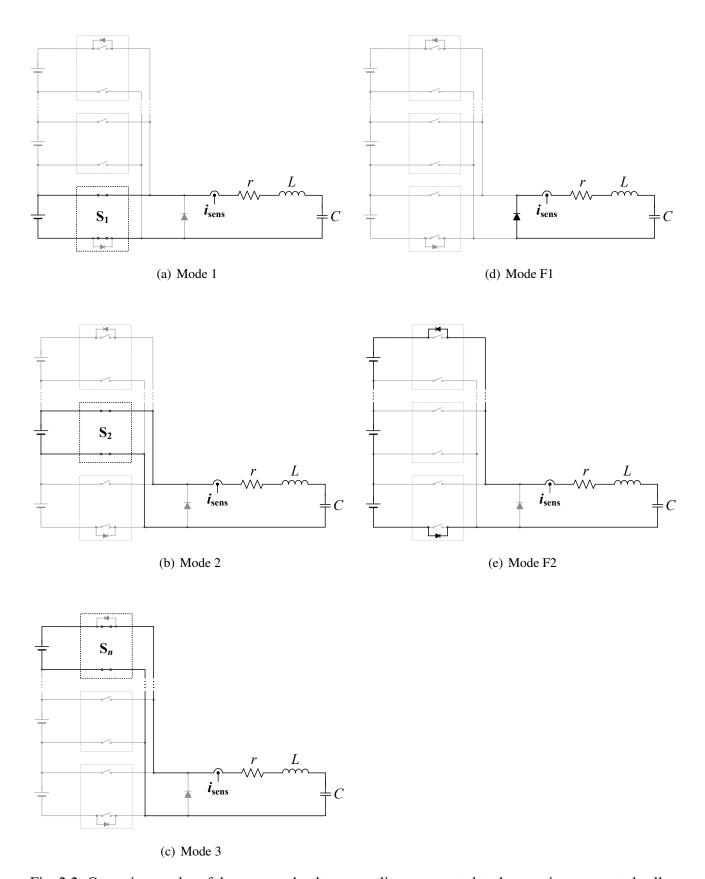

提案回路を,直列セル数が3(n=3)のバッテリモジュールに適用した場合には,5つの動作モードが存在する。Fig. 2.2(a)–(e) に,それぞれのモードを示す。

#### 均等化モード

Fig. 2.2(a)–(c) に示す動作モード (Mode 1–3) を、本論文では均等化モードと呼ぶ。このモードでは、それぞれのモード中において各バッテリセル電圧  $V_{Bj}$  (j=1–3) とキャパシタ C の電圧  $V_C$  の高電位側から低電位側へと均等化電流が流れる。この際、電流センサにより均等化電流を検出し、電流制限値  $i_{ref}$  [A] によるオン/オフ制御を行う。これは、バッテリセルの定格電流値を超えないようにするためであり、過大電流によるバッテリセルの劣化を防ぐ目的もある。なお、提案回路はバッテリモジュールが充放電状態である場合においても適用可能であるが、この場合には各バッテリの定格電流を超えないように提案回路の回路パラメータ、および充放電電流値を設定する必要がある。

#### 環流モード

全てのスイッチング素子がオフに切り換わった場合においても、インダクタLの電流はすぐには0にならず、しばらくの間流れ続ける。すべてのスイッチング素子がオフした状態で電流の流路が無くなってしまうと、インダクタLに高電圧が生じ、スイッチング素子を損傷させる可能性がある。これを防ぐため、ダイオードを挿入し環流させている (Fig. 2.2(d), (e))。このモード (Mode F1, F2) を、本論文では環流モードと呼ぶこととする。

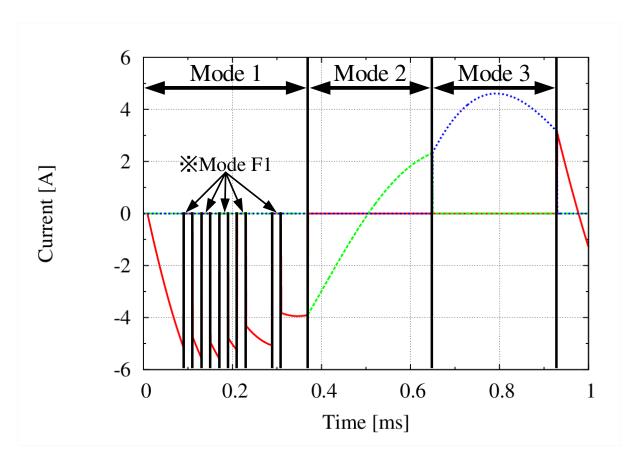

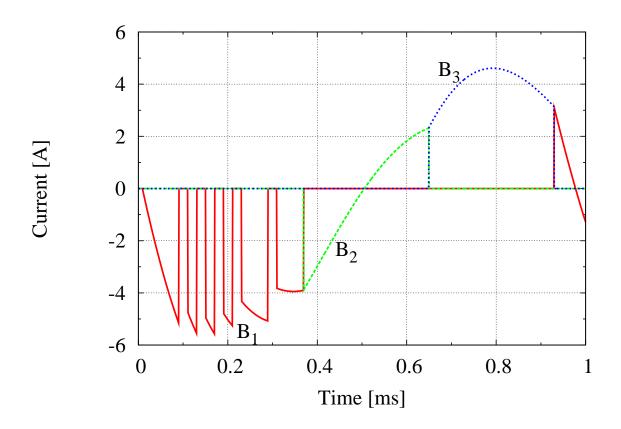

ここで,後述するセル数が n=3 の場合におけるシミュレーション結果の電流波形を用いて,各動作モードとの対応を示す。Fig. 2.3 に,均等化動作中における各セルの電流のシミュレーション結果を示す。Fig. 2.3 より,Mode 1-3 が順に切り替わっていることが確認できる。また,Mode 1 において電流が断続的となっているが,これは電流制限値  $i_{ref}=5.0$  A によるオン/オフ制御が行われているためである。Mode 1 では電流が立ち上がる過程で電流制限値の 5.0 A を超過したため,途中断続的に全てのスイッチング素子がオフとなる Mode F1 の環流モードとなっている。なお,本シミュレーション結果では電流が負方向に流れている際にスイッチング素子がオフとなったため Mode F1 が選択されているが,電流が正方向に流れている際にスイッチング素子がオフとなった場合は Mode F2 が選択されることとなる。

Fig. 2.2. Operating modes of the proposed voltage equalizer connected to three series-connected cells.

Fig. 2.3. Comparison between operating modes and simulation current waveforms.

#### 2.1.2 提案回路の特徴

提案回路の特徴は、抵抗を用いたパッシブ型 [12,13] と比較し、バッテリの蓄電エネルギーをより有効に活用することが可能である点にある。これにより、セル電圧の均等化を図ることでバッテリモジュールとしての充放電容量を最大限に活用できるだけでなく、セル電圧均等化動作時の消費電力をパッシブ型と比較して低減させ、均等化動作の効率向上が期待できる。

また、バッテリセルの直並列を切り替えることでセル電圧の均等化を図る方式 [14,15] では、一時的なエネルギー貯蔵素子を介さずに各バッテリセル間で直接的に電荷を移動させることが可能であることから効率面で優位性がある一方、各セル間の電圧差によってはスイッチング素子を切り替えた際に瞬間的に大電流が流れる可能性がある。提案回路では、バッテリセルとキャパシタCの間にインダクタLを挿入することで、接続するセルを切り替えた際の突入電流を軽減させている。加えて、スイッチング素子を用いてオン/オフ制御を行うことにより、均等化動作時に各バッテリセルに流れる電流を動的に制限することが可能である。

更に、提案回路ではバッテリセルとキャパシタCを並列にすることで電荷を移動させているため、電圧の高いセルから低いセルへと自動的に電流が流れ、各バッテリセルの電荷を移すことが可能である。そのため、セル電圧の均等化を図る際にセルごとの電圧値を測定する必要がなく、 $V_{Bj}$  (j=1-3) および $V_C$  それぞれの電位差の減少に比例して均等化電流も減少する。したがって、提案回路ではセル電圧均等化の制御を1つの電流センサのみで行うことが可能である。これにより、センサの数を大幅に減らすことが可能となる。

トランス等の磁性素子やキャパシタ等の蓄電素子を用いて各セル間でコンバータを形成することで各セル間で双方向に電荷の授受を行う方式 [16-47] では、一時的にエネルギーを蓄えるための受動素子がセル数に比例して多数必要となることから、回路規模が増大するといった課題があった。一方、提案回路でエネルギー貯蔵のために必要となる受動素子はインダクタLとキャパシタCがそれぞれ1つずつのみであることから、回路規模についても低減が期待される。

しかしながら、提案回路ではスイッチング素子がバッテリセルに対して並列に接続されているため、スイッチング素子が短絡モードで故障した場合にバッテリセルが短絡する可能性が考えられる。一般に、EDLCやリチウムイオンバッテリはエネルギー密度が高いという特徴があることから [48,49]、短絡故障の際には大電流が流れることで機器の故障を招くだけでなく、最悪の場合、発火・爆発の可能性がある。したがって、万一短絡モードで故障した際に、バッテリセルに大電流が流れることを防ぐ方法を検討する必要がある。本論文における回路の製作にあたっては、各バッテリセルと提案回路の間に自動復帰型ヒューズを挿入することでこれを防止した。なお、挿入したヒューズにより提案回路動作時の損失が増加する可能性があるが、使

Table 2.1. Comparison of the characteristics between conventional equalizers and the proposed equalizer [12–47].

| Equalizer type                               | Efficiency       | Current controllability | Size                     |

|----------------------------------------------|------------------|-------------------------|--------------------------|

| Power loss type [12, 13]                     | × (Passive type) | Possible                | 0                        |

| Series-parallel reconfigurable type [14, 15] | ○ (Active type)  | Impossible              | 2( <i>n</i> - 1)         |

| Bi-directional converter type [16–47]        | (Active type)    | Possible                | <i>n</i> or <i>n</i> - 1 |

| LC series circuit type (Proposed equalizer)  | O (Active type)  | Possible                | 2                        |

用したヒューズの抵抗分は約 $20 \,\mathrm{m}\Omega$ 程度であり、前述のインダクタLやキャパシタCの抵抗分rと比較しても影響は小さいと考えられる。また、遮断器等を用いた保護装置と比較してサイズやコストを大幅に削減できる点や、過電流が取り除かれた後の復旧の容易さから自動復帰型ヒューズを採用した。

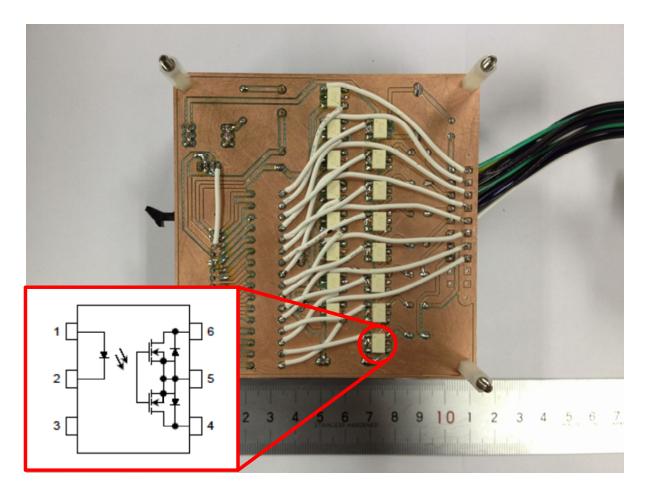

また,スイッチング素子の数が従来回路と比較して多くなっている。そのため,制御回路や ゲート駆動回路が複雑化する可能性がある。そこで,第2章から第4章の実機検討にあたっては, スイッチング素子に "Photo-MOS リレー [50]" を用いることでゲート駆動回路を簡素化した。

提案回路では従来回路と比較してスイッチング素子の数は増加しているが、アクティブ方式の採用による蓄電エネルギーの有効活用や均等化電流の動的な制御性のほか、一時的なエネルギー貯蔵のために必要な受動素子数の削減による回路規模の低減が期待される。以上、提案回路の特徴を従来回路とともにまとめると Table 2.1 のようになる。

#### 2.1.3 動作原理

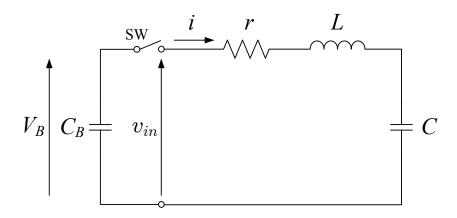

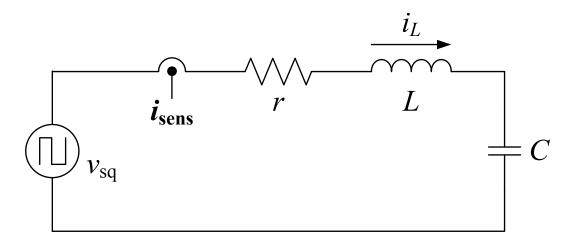

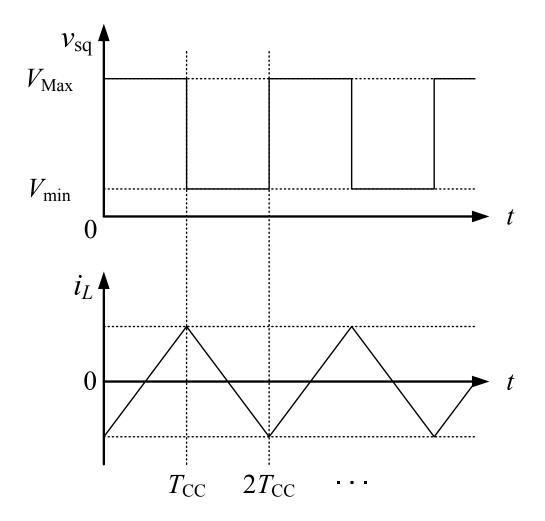

本節では、提案回路の動作原理について説明する。提案回路は、バッテリセルと LC 直列回路部の接続をセル切替周期  $T_{CC}$  [s] で順次切り替えることにより、セル電圧の均等化を図る方式である。ここで、提案回路の LC 直列回路部に着目すると、キャパシタ C および突入電流を防ぐために挿入したインダクタ L は、L および C の等価直列抵抗 (ESR: Equivalent Series Resistor) r [ $\Omega$ ] を考慮すると、単純な RLC 直列回路とみなすことが出来る。したがって、LC 直列回路部の各素子のパラメータの値によって提案回路の挙動は決定される。そこで、このパラメータを決定するにあたり、LC 直列回路部の回路解析を行う。

Fig. 2.4 に,LC 直列回路部の等価回路を示す。ここではまず,SW がオンした後,C が  $V_C=0$  の状態から V [V] まで充電されたときのバッテリセルの電圧変化量  $\Delta V_B$  を考える。簡易化のため,バッテリセルはキャパシタンス成分のみを考慮するものとし,その容量を  $C_B$  [F] とする。また,インダクタ L のインダクタンス成分を L [H],キャパシタ C のキャパシタンス成分を C [F] とする。 $V_C=V$  となったときのキャパシタ C の電荷 Q [C] について考えると,定常状態においては Q についるるので

$$V_C = \frac{q}{C}$$

$$\therefore q = CV_C \tag{2.1}$$

となる。このときの $\Delta V_B$ は

$$\Delta V_B|_{V_C:0\to V} = \frac{1}{C_B} \int i(t)dt$$

$$= \frac{q}{C_B} = \frac{C}{C_B}V$$

(2.2)

となり、 $\Delta V_B$  は C と  $C_B$  の比で表される。ここで、バッテリセルの容量  $C_B$  は、LC 直列回路のキャパシタ容量 C に比べて十分に大きく (一般に 100 倍から 1000 倍以上), $C \ll C_B$  の関係が成り立つとすれば

$$\Delta V_B \cong 0 \tag{2.3}$$

とすることが出来る。以降では、この仮定のもとでLC直列回路部の解析を行う。

$v_{in}$  と i は、Fig. 2.4 にキルヒホッフの電圧則を適用すると

$$v_{in} = ri(t) + L\frac{di(t)}{dt} + \frac{1}{C} \int i(t)dt$$

(2.4)

Fig. 2.4. Equivalent circuit of a part of the proposed cell voltage equalizer.

の関係にあることがわかる。これをラプラス変換すると

$$\mathcal{L}[v_{in}] = \frac{V_{in}}{s} = \left(r + sL + \frac{1}{sC}\right)I(s)$$

$$\therefore I(s) = \frac{V_{in}}{s\left(sL + r + \frac{1}{sC}\right)}$$

$$= \frac{V_{in}}{L\left\{\left(s + \frac{r}{2L}\right)^2 + \left(\frac{1}{LC} - \left(\frac{r}{2L}\right)^2\right)\right\}}$$

(2.5)

となる。このとき、r,L,C 各値の大小関係により、以下の3つの場合に分けて考えることができる。

(i)

$$r^2 < \frac{4L}{C}$$

のとき

$$\alpha = \frac{r}{2L}, \, \omega^2 = \frac{1}{LC} - \left(\frac{r}{2L}\right)^2 \,$$

とおくと

$$I(s) = \frac{V_{in}}{L\{(s+\alpha)^2 + \omega^2\}}$$

$$= \frac{V_{in}}{\omega L} \cdot \frac{\omega}{(s+\alpha)^2 + \omega^2}$$

$$\mathcal{L}^{-1}[I(s)] = i(t) = \frac{v_{in}}{\omega L} e^{-\alpha t} \sin \omega t \qquad (2.6)$$

(ii)

$$r^2 = \frac{4L}{C}$$

のとき

$$I(s) = \frac{V_{in}}{L(s+\alpha)^2}$$

$$= \frac{V_{in}}{L} \cdot \frac{1}{(s+\alpha)^2}$$

$$\mathcal{L}^{-1}[I(s)] = i(t) = \frac{v_{in}}{L} e^{-\alpha t} t$$

(2.7)

Table 2.2. Relationships among condition of r, angular frequency of the oscillation and  $t_{iMax}$ .

| Condition of $r$     | Angular frequency                                                                                | t                             |

|----------------------|--------------------------------------------------------------------------------------------------|-------------------------------|

| Condition of 7       | of the oscillation                                                                               | $t_{iMax}$                    |

| $r^2 < \frac{4L}{C}$ | $\sqrt{\frac{1}{LC} - \left(\frac{r}{2L}\right)^2}$                                              | $\frac{\varphi}{\omega}$      |

| $r^2 = \frac{4L}{C}$ | 0                                                                                                | $\frac{1}{\alpha}$            |

| $r^2 > \frac{4L}{C}$ | -                                                                                                | $\frac{\gamma}{\beta}$        |

|                      | $\left(\varphi = \tan^{-1}\frac{\omega}{\alpha}, \gamma = \tan^{-1}\frac{\omega}{\alpha}\right)$ | $h^{-1} \frac{\beta}{\alpha}$ |

(iii)

$$r^2 > \frac{4L}{C}$$

のとき

$$\beta = \left(\frac{r}{2L}\right)^2 - \frac{1}{LC}$$

とおくと

$$I(s) = \frac{V_{in}}{L\{(s+\alpha)^2 - \beta^2\}}$$

$$= \frac{V_{in}}{\beta L} \cdot \frac{\beta}{(s+\alpha)^2 - \beta^2}$$

$$\mathcal{L}^{-1}[I(s)] = i(t) = \frac{v_{in}}{\beta L} e^{-\alpha t} \sinh \beta t$$

(2.8)

したがって、rと過渡状態における振動の角周波数 $\omega$  [rad/s]、およびiが最大となるときの時刻  $t_{iMax}$  [s] の関係性についてまとめると Table 2.2 のようになる。

ここで、電流の過渡特性はLおよびCの値により決定される。電流の立ち上がりが急峻すぎると、制御周波数  $f_{cnt}$  [Hz] による電流制限値  $i_{ref}$  [A] での制限が困難となる。すなわち、LおよびCの値は  $i_{ref}$  や  $f_{cnt}$  の値に依存する。提案回路では電流の制限値を設けて制御を行うことを想定していることから、回路定数の設計に際しては、電流値i が電流制限値 $i_{ref}$  付近で制御可能となるようなパラメータを選択することが求められる。

次節では、上記パラメータの設計手法について説明する。

## 2.2 各回路パラメータの設計法

前節で述べたように、提案回路で均等化電流の制限を行うためには、適切な回路パラメータを選択することが求められる。本節では、後述のシミュレーションで用いる回路パラメータ (Table 2.9) の導出方法について説明する。

#### **2.2.1** 回路素子 *L*, *C* の設計指針

シミュレーション回路で要求される回路条件を Table 2.3 に示す。この条件より,最大電圧 4.0 V を印加した際に,制御周波数  $f_{\rm cnt}=50~{\rm kHz}$  より,制御周期  $T_{\rm cnt}=1/f_{\rm cnt}=20~{\rm \mu s}$  で電流制限値 5.0 A を超えないような r,L,C の値を設定すれば良い。具体的には  $\frac{e}{\omega}\geq 20~{\rm \mu s}$ ,また  $i(20~{\rm \mu s})\leq 5.0~{\rm A}$  を満たすパラメータを求める。ここで,一般にキャパシタ C が大きいほど LC 直列回路部に蓄えられる電力が大きくなるため,提案回路の均等化時間も短くなると考えられる。一方で,C を大きくしすぎるとキャパシタ C の体積が増加し,回路規模が増大する可能性がある。そこで,本論文におけるキャパシタ C の選定にあたっては,前述の  $\frac{e}{\omega}\geq 20~{\rm \mu s}$ ,また  $i(20~{\rm \mu s})\leq 5.0~{\rm A}$  を満たしつつ,回路規模が肥大化しない小型の電解コンデンサ等で実現可能な値とした。以上の条件から,これらを満たすパラメータを表計算ソフトを用いて算出した。算出した各値はそれぞれ, $C=100~{\rm m}$ 0、 $C=100~{\rm m}$ 1、 $C=100~{\rm m}$ 2、 $C=100~{\rm m}$ 3 に対していると

$$\frac{\varphi}{\omega} = \frac{\tan^{-1}\left(\frac{\sqrt{\frac{1}{LC} - \left(\frac{r}{2L}\right)^2}}{\frac{r}{2L}}\right)}{\sqrt{\frac{1}{LC} - \left(\frac{r}{2L}\right)^2}} = 220 \,\mu\text{s}$$

(2.9)

$$i(20 \,\mu\text{s}) = \frac{V_{in}}{L\sqrt{\frac{1}{LC} - \left(\frac{r}{2L}\right)^2}} e^{-\frac{r}{2L}t} \cdot \sin\left(\sqrt{\frac{1}{LC} - \left(\frac{r}{2L}\right)^2}t\right)$$

= 1.56 A (2.10)

となり、Table 2.3 に示した、要求される回路条件を満足していることがわかる。ここで、式 (2.10) により求められた  $i(20~\mu s)=1.56~A$  とは、最大電圧 4.0~V を印加した際に  $20~\mu s$  で変化する電流値を表している。今回のシミュレーションでは制御周波数  $f_{\rm cnt}=50~{\rm kHz}$  としたために、制御周期  $T_{\rm cnt}=1/f_{\rm cnt}=20~\mu s$  の時間変化の中で電流値が電流制限値  $i_{\rm ref}=5.0~A$  以上に変化しないように設定する必要がある。しかしながら、本論文では電流制御を  $i_{\rm ref}$  をしきい値としたオン/オフ制御を採用しているため、 $i(20~\mu s)$  が  $i_{\rm ref}$  に近い値になるように設定すると、制御のタイミングにより  $i_{\rm ref}$  を大幅に超える電流が流れる可能性がある。そこで、これを防止するために $i(20~\mu s)=1.56~A$  という 5.0~A から大きなマージンをとった値を設定した。これにより前述のような  $i_{\rm ref}$  をしきい値としたオン/オフ制御を用いた場合でも、i を最大で 5.0~A 1.56  $\cong$  6.6~A 以内

Table 2.3. Required specifications of the simulation circuit.

| Maximum input voltage       | 4.0 V  |

|-----------------------------|--------|

| Current limit value         | 5.0 A  |

| Control frequency $f_{cnt}$ | 50 kHz |

に制限可能である。ここで,設計上はiが最大で 6.6 A 程度流れる可能性があると考えられるが,これはキャパシタCの電圧  $V_C$ が 0 V である均等化動作開始直後のみに限定されており,均等化動作が進行すると $V_C>0$  となるためiの最大値は 6.6 A よりも小さな値となる。また,一般にセル電圧均等化回路の均等化動作時に流れる電流はバッテリセルの定格電流値に対して小さい値となるように設計されることが多く [16,17],前述の電流制限値 $i_{ref}$  についても同様に設定しているため,オン/オフ制御を用いたことでiが $i_{ref}$  を多少超過したとしても大きな問題は無いが,本論文のようにオン/オフ制御を用いる場合には $i_{ref}$  +  $i(T_{cnt})$  がバッテリセルの定格電流値を超えないように設計する必要がある。なお,より厳密な電流制限を行う場合には各回路パラメータの設計方針のほか,制御周期 $T_{cnt}$ の高速化や電流の予測制御などを取り入れることが有効であると考えられる。

また、実機ではバッテリセルの劣化による ESR の増加も考えられるが、劣化による ESR の増加量はrと比較して十分小さく、これによる電流制御への影響は小さい。

#### **2.2.2** セル切替周期 T<sub>CC</sub> の設計指針

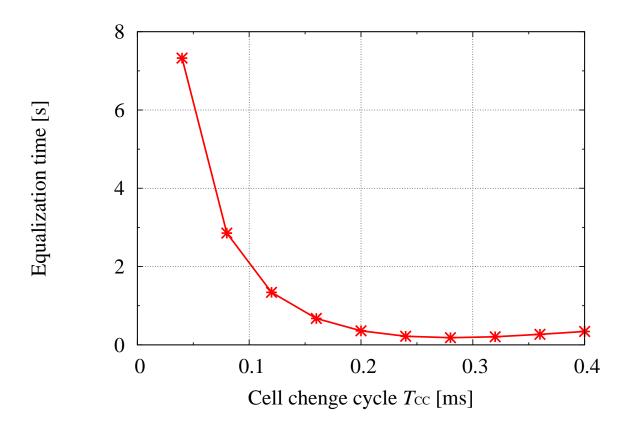

次に、提案回路の動作特性を決定する一因であるセル切替周期  $T_{CC}$  の設計指針を示す。 $T_{CC}$  の設計に際しては提案回路の理論解析により最適となる値を導出するべきであると考えられるが、Fig. 2.3 に示したように提案回路の均等化動作は常に過渡状態の連続であるため、理論式は複雑なものとなり、簡易的に解析を行うことは困難である。そのため、本論文ではセル切替周期  $T_{CC}$  と均等化時間 (本章では各セル電圧の標準偏差が 10~mV となるまでの時間と定義) の関係に着目し、シミュレーションおよび実機実験により両者の関係性について検証し、その傾向を分析することで  $T_{CC}$  の設計指針を示すこととした。

#### セル数の違いによる影響

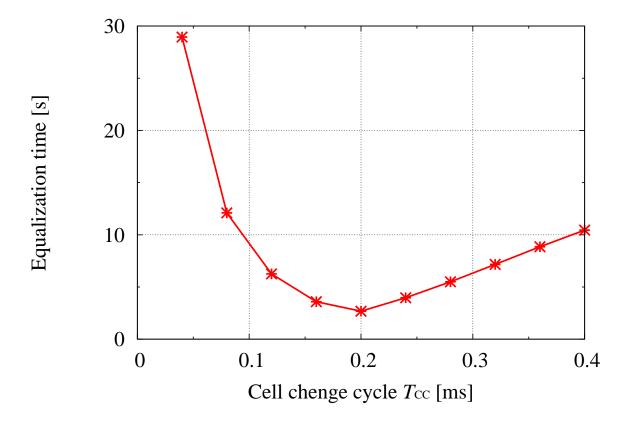

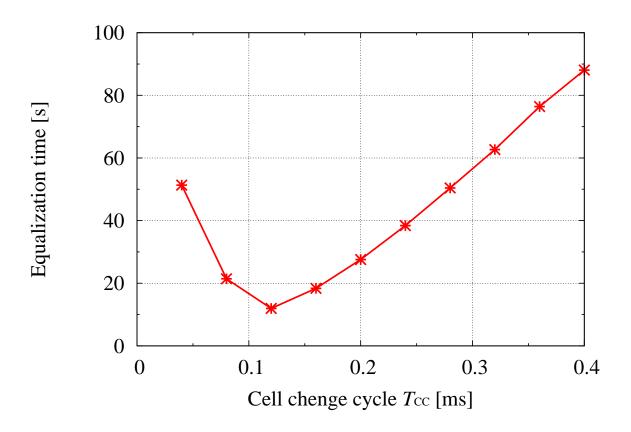

まず、後述のシミュレーションで用いる回路パラメータ (Table 2.9) を利用し、セル数を 3 セル、8 セル、16 セルと変化させた際のセル切替周期  $T_{CC}$  と均等化時間と関係性について検討した。シミュレーション条件を Table 2.4 に示す。本シミュレーションでは、セル数 n と  $T_{CC}$  以外のパラメータを同一としたときに、 $T_{CC}$  を 0.04–0.40 ms で変化させた際の均等化時間をシミュレーションにより求めた。

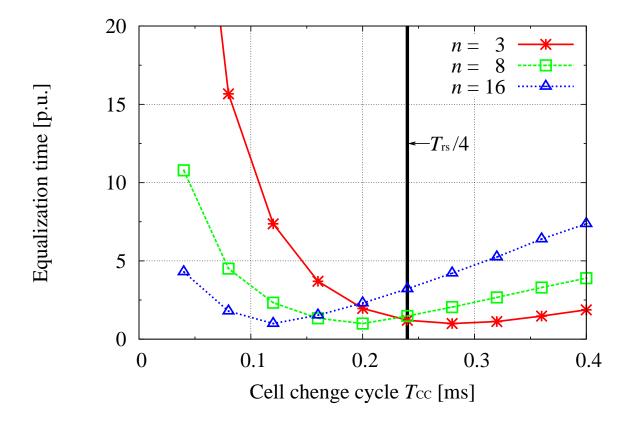

3 セル、8 セル、16 セルのシミュレーション結果をそれぞれ Fig. 2.5–2.7 に示す。Fig. 2.5–2.7 より、3 セル、8 セル、16 セルのいずれも  $T_{\rm CC}$  の変化に伴って均等化時間が変化することがわかる。また、均等化時間が最小となる  $T_{\rm CC}$  に対して、 $T_{\rm CC}$  が小さい場合と大きい場合のどちらも均等化時間は増加することが確認された。ここで、セル数 n に対する  $T_{\rm CC}$  と均等化時間の関係を比較しやすくするため、それぞれのシミュレーション結果について、最小の均等化時間を1としたときの各  $T_{\rm CC}$  に対する均等化時間の相対値を Fig. 2.8 にまとめて示す。Fig. 2.8 より、均等化時間が最小となる  $T_{\rm CC}$  はセル数によって変化することがわかる。ここで,LC 直列回路部の共振周期  $T_{\rm rs}$  に着目すると、 $T_{\rm rs}$  =  $2\pi\sqrt{LC}$   $\cong$  0.96 ms であるので、その 1/4 周期は 0.24 ms となる。この  $T_{\rm rs}$ /4 = 0.24 ms と Fig. 2.8 の結果を比較すると、 $T_{\rm CC}$  = 0.24 ms とした際の均等化時間は、3 セル、8 セル、16 セルのいずれの場合においても、それぞれ最小均等化時間の概ね 2–4 倍以内に収まっていることが確認できる。

Table 2.4. Circuit parameters in the simulations to derive the cell change cycle  $T_{\rm CC}$ .

| Number of cells <i>n</i>            | 3, 8, 16               |

|-------------------------------------|------------------------|

| Battery cell capacity               | 50 mF                  |

| ESR of each battery cell            | $100~\text{m}\Omega$   |

| Initial voltage of $V_{\rm B1-B3}$  | 1.30-2.90 V            |

| (under 3 cells condition)           | (1.30 V step)          |

| Initial voltage of $V_{\rm B1-B8}$  | 0.50–4.00 V            |

| (under 8 cells condition)           | (0.50 V step)          |

| Initial voltage of $V_{\rm B1-B16}$ | 0.25–4.00 V            |

| (under 16 cells condition)          | (0.25 V step)          |

| ESR of inductor and capacitor $r$   | $100~\mathrm{m}\Omega$ |

| Inductance L                        | $50  \mu \mathrm{H}$   |

| Capacitance C                       | $470\mu\mathrm{F}$     |

| Control frequency $f_{cnt}$         | 50 kHz                 |

| Cell change cycle $T_{\rm CC}$      | 0.04–0.40 ms           |

|                                     | (0.04 ms step)         |

| Current limit value $i_{ref}$       | 5.0 A                  |

|                                     |                        |

Fig. 2.5. Simulation results of the relationship between the cell change cycle  $T_{\rm CC}$  and the equalization time under three cells condition.

Fig. 2.6. Simulation results of the relationship between the cell change cycle  $T_{\rm CC}$  and the equalization time under eight cells condition.

Fig. 2.7. Simulation results of the relationship between the cell change cycle  $T_{\rm CC}$  and the equalization time under sixteen cells condition.

Fig. 2.8. Comparison among the simulation results of the relationships on the number of cells *n*.

#### LC 直列回路部の時定数の違いによる影響

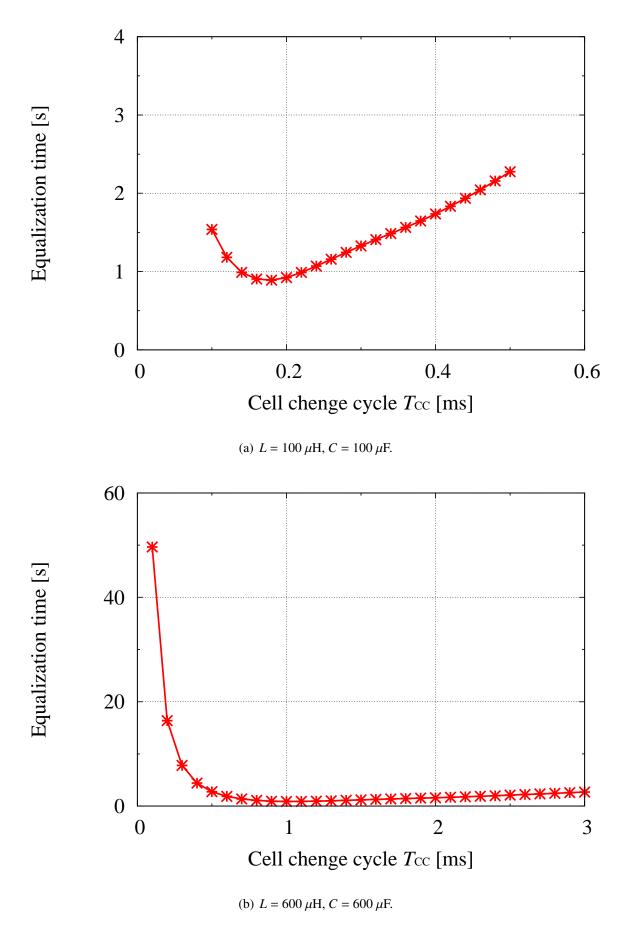

次に、インダクタ L とキャパシタ C の値に起因する L C 直列回路部の時定数と均等化時間の関係性について検討した。シミュレーション条件として、インダクタンス L とキャパシタンス C の組み合わせがそれぞれ  $100\,\mu$ ,  $600\,\mu$  の 2 つの場合について検証した。これらは、時定数の差が明確であり、かつシミュレーションに要する時間が長すぎない値となるように選定した。シミュレーション条件を Table 2.5 に示す。本シミュレーションでは、L E C の各組み合わせに対し、 $100\,\mu$  のときは  $T_{CC}$  を 0.10–0.50 ms, $600\,\mu$  のときは  $T_{CC}$  を 0.10–3.00 ms で変化させた際の均等化時間をそれぞれシミュレーションにより求めた。

Fig. 2.9(a) に  $L = 100 \,\mu\text{H}$ ,  $C = 100 \,\mu\text{F}$  のときのシミュレーション結果を示す。Fig. 2.9(a) より、均等化時間が最小となる  $T_{CC}$  の値は 0.18 ms であった。

同様に,  $L = 600 \, \mu\text{H}$ ,  $C = 600 \, \mu\text{F}$  のときについても検討した。Fig. 2.9(b) にシミュレーション結果を示す。Fig. 2.9(b) より、均等化時間が最小となる  $T_{CC}$  の値は 1.00 ms であった。

ここで,LC 直列回路部の共振周期  $T_{\rm rs}$  に着目すると, $L=100~\mu{\rm H}$ , $C=100~\mu{\rm F}$  の組み合わせでは  $T_{\rm rs}=2\pi\sqrt{LC}\cong0.63~{\rm ms}$  であるので,その 1/4 周期は  $0.16~{\rm ms}$  となる。同様に, $L=600~\mu{\rm H}$ , $C=600~\mu{\rm F}$  の組み合わせでは  $T_{\rm rs}=2\pi\sqrt{LC}\cong3.77~{\rm ms}$  であるので,その 1/4 周期は  $0.94~{\rm ms}$  となる。ここで,これらの値と均等化時間が最小となったときの  $T_{\rm CC}$  を比較すると,概ね一致していることが確認された。

Table 2.5. Circuit parameters in the simulations to derive the cell change cycle  $T_{\rm CC}$  considering the time constant of the LC series circuit.

| Number of cells <i>n</i>                      | 3              |

|-----------------------------------------------|----------------|

| Battery cell capacity                         | 50 mF          |

| Initial voltage of $V_{\rm B1-B3}$            | 1.00-3.00 V    |

|                                               | (1.00 V step)  |

| ESR of inductor and capacitor $r$             | 1 Ω            |

| Inductance L                                  | 100, 600 μΗ    |

| Capacitance C                                 | 100, 600 μF    |

| Control frequency $f_{cnt}$                   | 50 kHz         |

| Cell change cycle $T_{\rm CC}$                | 0.10–0.50 ms   |

| $(L = 100 \mu\text{H},  C = 100 \mu\text{F})$ | (0.02 ms step) |

| Cell change cycle $T_{\rm CC}$                | 0.10–3.00 ms   |

| $(L = 600 \mu\text{H},  C = 600 \mu\text{F})$ | (0.10 ms step) |

| Current limit value $i_{ref}$                 | 5.0 A          |

Fig. 2.9. Simulation results of the relationship between the cell change cycle  $T_{\rm CC}$  and the time constant of the LC series circuit.

#### LC 直列回路部の過渡応答特性の違いによる影響

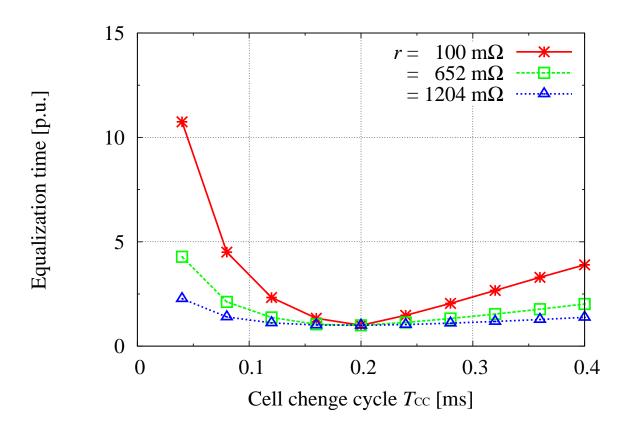

また,インダクタ Lとキャパシタ C,およびそれぞれの ESR 分 r の値に起因する LC 直列回路 部の過渡応答特性と均等化時間の関係性についてもシミュレーションにより検討した。シミュレーション条件を Table 2.6 に示す。シミュレーションでは,インダクタンス  $L=50~\mu H$ ,キャパシタンス  $C=470~\mu F$  固定とし,LC 直列回路部の過渡応答特性が振動減衰系  $(r<\sqrt{\frac{4L}{C}})$ ,臨界減衰系  $(r=\sqrt{\frac{4L}{C}})$ ,過減衰系  $(r>\sqrt{\frac{4L}{C}})$  のそれぞれとなる r=100, 652,  $1204~m\Omega$  の場合について検証した。

シミュレーション結果を Fig. 2.10 に示す。ここで, $i_{ref}$  による  $T_{CC}$  と均等化時間の関係性を比較しやすくするため,Fig. 2.10 ではそれぞれの  $i_{ref}$  に対する結果について,最小の均等化時間を 1 としたときの各  $T_{CC}$  に対する均等化時間の相対値を示した。Fig. 2.10 より,r を変化させ LC 直列回路部の過渡応答特性が変化した際に,均等化時間が最小となる  $T_{CC}$  の変化は認められなかった。したがって,LC 直列回路部の過渡応答特性の違いがセル切替周期  $T_{CC}$  と均等化時間の関係性に与える影響は小さいことが示唆された。

Table 2.6. Circuit parameters in the simulations to derive the cell change cycle  $T_{\rm CC}$  considering the transient response characteristics of the LC series circuit.

| Number of cells <i>n</i>                                       | 8                              |

|----------------------------------------------------------------|--------------------------------|

| Battery cell capacity                                          | 50 mF                          |

| ESR of each battery cell                                       | $100~\mathrm{m}\Omega$         |

| Initial voltage of $V_{\rm B1-B8}$                             | 0.50–4.00 V                    |

|                                                                | (0.50 V step)                  |

| ESR of inductor and capacitor r                                | $100,652,1204 \text{ m}\Omega$ |

| Inductance L                                                   | 50 μH                          |

| Capacitance C                                                  | $470\mu\mathrm{F}$             |

|                                                                |                                |

| Control frequency $f_{cnt}$                                    | 50 kHz                         |

| 1                                                              | 50 kHz<br>0.04–0.40 ms         |

| Control frequency $f_{\rm cnt}$ Cell change cycle $T_{\rm CC}$ |                                |

|                                                                | 0.04–0.40 ms                   |

Fig. 2.10. Comparison among the relationships between the cell change cycle  $T_{\rm CC}$  and the transient response characteristics of the LC series circuit.

#### デッドタイムによる影響

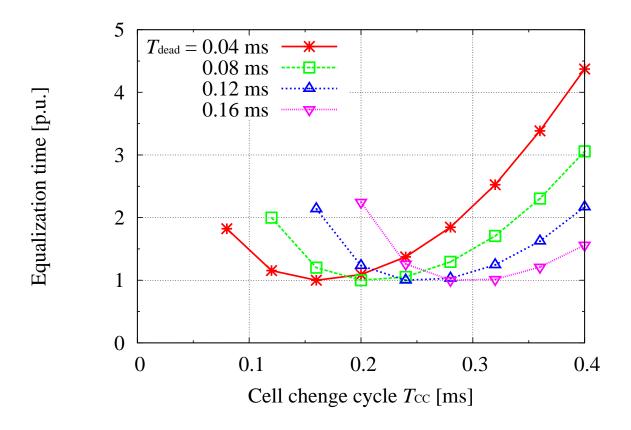

実機実験においては,各スイッチング素子間でのバッテリセルの短絡を防止するため,各均等化モードの切り替わりのタイミングで全てのスイッチング素子がオフとなるようにデッドタイムを挿入している。本論文では, $T_{CC}$ を削るようにデッドタイムを挿入していることから,このデッドタイムも均等化時間へ影響を与える可能性がある。そこで,セル数は8セル固定とし,デッドタイム  $T_{dead}$  とセル切替周期  $T_{CC}$  を変化させた際の均等化時間をシミュレーションにより求めた。シミュレーション条件 Table 2.7 に示す。

シミュレーション結果を Fig. 2.11 に示す。ここで, $T_{\rm dead}$  による  $T_{\rm CC}$  と均等化時間の関係を比較しやすくするため,Fig. 2.11 ではそれぞれの  $T_{\rm dead}$  に対する結果について,最小の均等化時間を 1 としたときの各  $T_{\rm CC}$  に対する均等化時間の相対値を示した。 Fig. 2.11 より, $T_{\rm dead}$  が大きくなるにつれて,均等化時間が最小となる  $T_{\rm CC}$  も大きくなっていることがわかる。なお,Fig. 2.6 に示したデッドタイム無しのシミュレーション結果と比較すると,Fig. 2.11 における  $T_{\rm dead}$  = 0.04 ms のときの結果の方が,均等化時間が最小となる  $T_{\rm CC}$  が 0.20 ms から 0.16 ms と小さく

Table 2.7. Circuit parameters in the simulations to derive the cell change cycle  $T_{\rm CC}$  inserted the dead-time  $T_{\rm dead}$ .

| Number of cells <i>n</i>           | 8              |

|------------------------------------|----------------|

| Battery cell capacity              | 50 mF          |

| ESR of each battery cell           | 100 mΩ         |

| Initial voltage of $V_{\rm B1-B8}$ | 0.50-4.00 V    |

|                                    | (0.50 V step)  |

| ESR of inductor and capacitor r    | 100 mΩ         |

| Inductance L                       | 50 μH          |

| Capacitance C                      | 470 μF         |

| Control frequency $f_{cnt}$        | 50 kHz         |

| Cell change cycle $T_{\rm CC}$     | 0.04–0.40 ms   |

|                                    | (0.04 ms step) |

| Dead-time $T_{\rm dead}$           | 0.04–0.16 ms   |

|                                    | (0.04 ms step) |

| Current limit value $i_{ref}$      | 5.0 A          |

|                                    |                |

Fig. 2.11. Comparison among the relationships between the cell change cycle  $T_{\rm CC}$  and the dead-time  $T_{\rm dead}$ .

なっている。これは、デッドタイムを挿入したことにより各バッテリセルに流れる電流のモードが変化した影響が、均等化時間にも現れたものと考えられる。しかしながら、全体的な傾向としては $T_{\rm dead}$ の増加に比例して均等化時間も増加することが確認された。

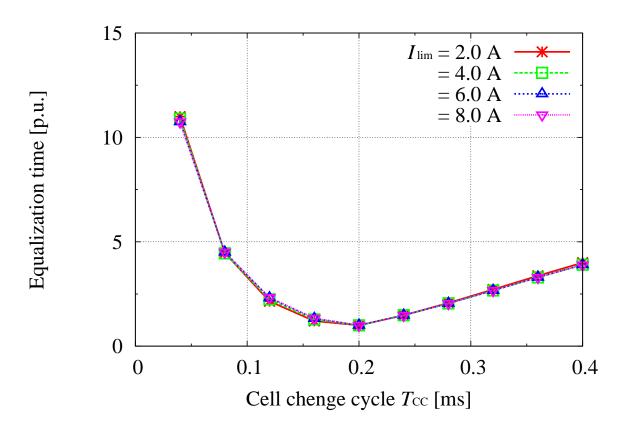

#### 電流制限値による影響

提案回路の特徴として,電流制限値  $i_{ref}$  による均等化電流の動的な制限が挙げられる。そのため,Fig. 2.3 に示したように  $i_{ref}$  の値によって均等化動作の挙動が変化することから,セル切替周期  $T_{CC}$  と均等化時間の関係性にも影響を与える可能性がある。そこで,電流制限値  $i_{ref}$  を変化させた際のセル切替周期  $T_{CC}$  と均等化時間の関係性について,シミュレーションにより検証した。シミュレーション条件 Table 2.8 に示す。

シミュレーション結果を Fig. 2.12 に示す。ここで, $i_{ref}$  による  $T_{CC}$  と均等化時間の関係を比較しやすくするため,Fig. 2.12 ではそれぞれの  $i_{ref}$  に対する結果について,最小の均等化時間を 1 としたときの各  $T_{CC}$  に対する均等化時間の相対値を示した。Fig. 2.12 より, $i_{ref}$  を変化させた際の均等化時間が最小となる  $T_{CC}$  に大きな変化は認められなかった。したがって,電流制限値  $i_{ref}$  がセル切替周期  $T_{CC}$  と均等化時間の関係性に与える影響は小さいことが示唆された。

Table 2.8. Circuit parameters in the simulations to derive the cell change cycle  $T_{\rm CC}$  considering the current limit value  $i_{\rm ref}$ .

| Number of cells <i>n</i>               | 8                      |

|----------------------------------------|------------------------|

| Battery cell capacity                  | 50 mF                  |

| ESR of each battery cell               | $100~\mathrm{m}\Omega$ |

| Initial voltage of $V_{\rm B1-B8}$     | 0.50-4.00 V            |

|                                        | (0.50 V step)          |

| ESR of inductor and capacitor <i>r</i> | 100 mΩ                 |

| Inductance L                           | 50 μH                  |

| Capacitance C                          | 470 μF                 |

| Control frequency $f_{cnt}$            | 50 kHz                 |

| Cell change cycle $T_{\rm CC}$         | 0.04–0.40 ms           |

|                                        | (0.04 ms step)         |

| Current limit value $i_{ref}$          | 2.0-8.0 A              |

|                                        | (2.0 A step)           |

|                                        |                        |

Fig. 2.12. Comparison among the relationships between the current limit value  $i_{ref}$  and the equalization time.

#### シミュレーションによる検証結果の分析

前述のシミュレーション結果から,提案回路では $T_{\rm CC}$ を LC 直列回路部の共振周期 $T_{\rm rs}$ の 1/4 となるように設定することで,セル数n ならびに時定数が変化した場合でも均等化時間を概ね小さくできることが示唆された。また,デッドタイム $T_{\rm dead}$ の増加に比例して均等化時間も増加することも確認された。したがって, $T_{\rm CC}=T_{\rm rs}/4+T_{\rm dead}$ (ただし, $T_{\rm rs}=2\pi\sqrt{LC}$ )という指針を基に $T_{\rm CC}$ を設定することで,均等化時間を大幅に増加させることなく,容易に $T_{\rm CC}$ の設計が可能であると考えられる。

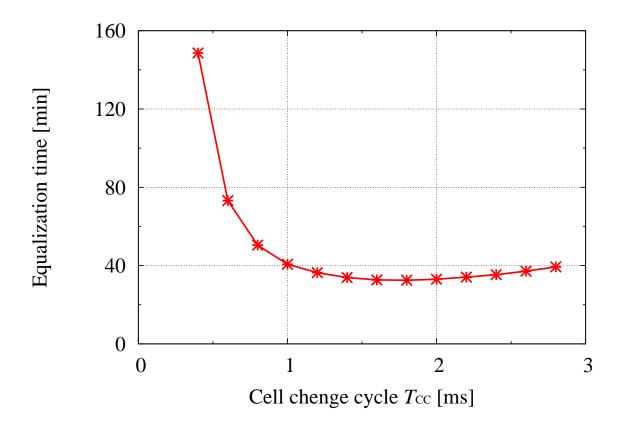

#### 実機実験による分析結果の検証

前述のシミュレーション検証の結果から, $T_{\rm CC}=T_{\rm rs}/4+T_{\rm dead}$ (ただし, $T_{\rm rs}=2\pi\sqrt{LC}$ )という指針を基に  $T_{\rm CC}$  を設定することで,均等化時間を大幅に増加させることなく,容易に  $T_{\rm CC}$  の設計が可能であることが示唆された。そこで,前述の分析結果の妥当性について,後述の実機実験で用いる回路パラメータ (Table 2.13) を利用し,セル切替周期  $T_{\rm CC}$  を 0.40–2.80 ms で 0.20 ms 毎に変化させた場合の均等化時間の変化について検証を行った。このとき r=349 m $\Omega$  であり, $r<\sqrt{\frac{4L}{C}}$  を満たしている。また,前述の分析結果より  $T_{\rm CC}$  は

$$T_{\text{CC}} = T_{\text{rs}}/4 + T_{\text{dead}}$$

= 1.52 + 0.10 \approx 1.6 [ms] (2.11)

とすることが妥当である。

Fig. 2.13 に実験結果を示す。Fig. 2.13 より,均等化時間が最小となる  $T_{CC}$  の値は 1.8 ms であった。これは,前述のシミュレーション分析の結果から得られた  $T_{CC}$  = 1.6 ms と概ね一致している。また, $T_{CC}$  = 1.6 ms のときの均等化時間は 32.7 min,均等化時間が最小となった  $T_{CC}$  = 1.8 ms のときの均等化時間は 32.5 min であり,その差は 1 %未満であった。したがって,提案回路ではセル切替周期  $T_{CC}$  を  $T_{rs}$  / 4 +  $T_{dead}$  (ただし, $T_{rs}$  =  $2\pi\sqrt{LC}$ ) という指針を基に設計することで,均等化時間を大幅に増加させることなく,容易に  $T_{CC}$  の設計が可能であることが実機実験の結果からも明らかとなった。

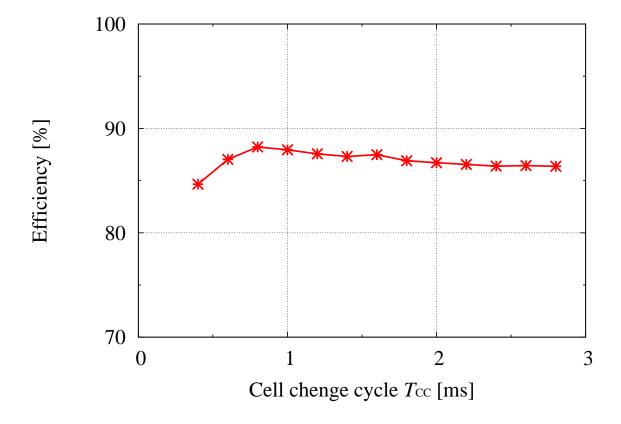

また、Fig. 2.14 にそれぞれの  $T_{CC}$  における均等化動作の効率を示す。なお、効率の算出にあたっては後述の式 (2.12) を用いて、均等化動作前後の静電エネルギーの差から求めた。Fig. 2.14 より、 $T_{CC}$  により均等化動作時の効率は多少変動するものの、概ね 85–90 % の範囲で推移していた。特に、均等化時間が大きく変化していない  $T_{CC} > 1.0$  ms の領域においては、均等化動作時の効率についても大きな変化は認められなかった。

Fig. 2.13. Experimental results of the relationships between the equalization time and the cell change cycle  $T_{\rm CC}$ .

Fig. 2.14. Experimental results of the relationships between the efficiency and the cell change cycle  $T_{\rm CC}$ .

## 2.3 シミュレーションによる動作特性の検証

提案回路の有用性について検討するため、バッテリモジュールの模擬としてキャパシタンス成分と ESR のみを考慮したバッテリセルを 3 セル直列に接続した場合、8 セル直列に接続した場合、および 16 セル直列に接続した場合のそれぞれについてセル電圧均等化動作のシミュレーションを行った。本節のシミュレーション検証ではセル数の違いによる動作特性への影響についても検討するため、均等化動作の最小数である 3 セルと、一般的なセル電圧均等化回路が対象としている 8 セルおよび 16 セルの 3 種類についてシミュレーションを行った。

本シミュレーションにおけるパラメータを Table 2.9, Table 2.10, および Table 2.11 に示す。ここで、シミュレーション時の回路パラメータは、後述の実機実験時の回路パラメータと異なる値を用いた。これは、提案回路の均等化動作の特性上、シミュレーションにおいて実機実験と同じ回路パラメータを用いた場合には膨大なシミュレーション時間を要するためである。本論文のシミュレーションでは提案回路の基本動作特性の検証を目的としていることから、以降のシミュレーションにおいては実機実験時と異なる回路パラメータを用いた。

また、本論文のシミュレーションおよび実機実験では、初期電圧のばらつきを SOC(State Of Charge) に換算して 10-90 % 程度と大きく設定している。これは、通常のバッテリモジュールの運用ではセル電圧のばらつきが小さい段階から均等化動作を行うことが一般的であるが、本論文では各セル間で電圧のばらつきが大きい場合においても提案回路の均等化動作が可能であることを示すために前述のような初期条件を設定した。

Table 2.9. Circuit parameters in the simulation for the three series-connected cells.

| Number of cells <i>n</i>           | 3                      |

|------------------------------------|------------------------|

| Battery cell capacity              | 50 mF                  |

| ESR of each battery cell           | $100~\mathrm{m}\Omega$ |

| Initial voltage of $V_{\rm B1-B3}$ | 1.30-2.90 V            |

|                                    | (1.30 V step)          |

| ESR of inductor and capacitor $r$  | $100~\text{m}\Omega$   |

| Inductance L                       | 50 μH                  |

| Capacitance C                      | 470 μF                 |

| Control frequency $f_{cnt}$        | 50 kHz                 |

| Cell change cycle $T_{\rm CC}$     | 0.24 ms                |

| Current limit value $i_{ref}$      | 5.0 A                  |

|                                    |                        |

Table 2.10. Circuit parameters in the simulation for the eight series-connected cells.

| Number of cells <i>n</i>               | 8                      |

|----------------------------------------|------------------------|

| Battery cell capacity                  | 50 mF                  |

| ESR of each battery cell               | $100~\mathrm{m}\Omega$ |

| Initial voltage of $V_{\rm B1-B8}$     | 0.50–4.00 V            |

|                                        | (0.50 V step)          |

| ESR of inductor and capacitor <i>r</i> | 100 mΩ                 |

| Inductance L                           | 50 μH                  |

| Capacitance C                          | 470 μF                 |

| Control frequency $f_{cnt}$            | 50 kHz                 |

| Cell change cycle $T_{\rm CC}$         | 0.24 ms                |

| Current limit value $i_{ref}$          | 5.0 A                  |

|                                        |                        |

Table 2.11. Circuit parameters in the simulation for the sixteen series-connected cells.

| Number of cells <i>n</i>            | 16                     |

|-------------------------------------|------------------------|

| Battery cell capacity               | 50 mF                  |

| ESR of each battery cell            | $100~\mathrm{m}\Omega$ |

| Initial voltage of $V_{\rm B1-B16}$ | 0.25–4.00 V            |

|                                     | (0.25 V step)          |

| ESR of inductor and capacitor $r$   | $100~\mathrm{m}\Omega$ |

| Inductance L                        | 50 μH                  |

| Capacitance C                       | 470 μF                 |

| Control frequency $f_{cnt}$         | 50 kHz                 |

| Cell change cycle $T_{\rm CC}$      | 0.24 ms                |

| Current limit value $i_{ref}$       | 5.0 A                  |

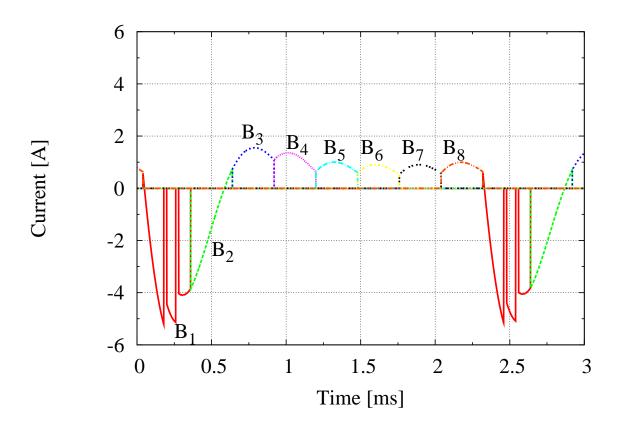

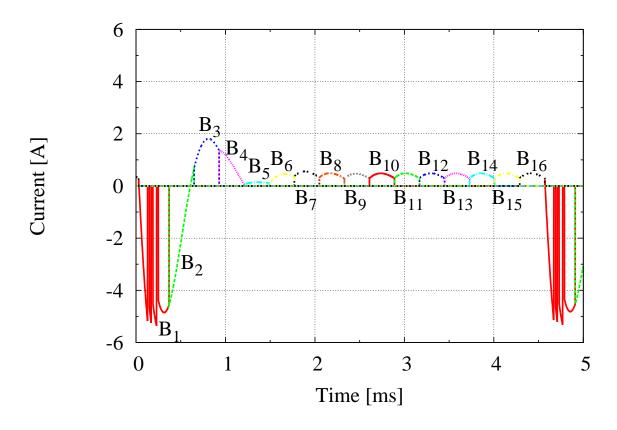

Fig. 2.15, 2.16, 2.17 にそれぞれバッテリセルを 3 セル,8 セル,16 セル直列にした場合における各セル電流のシミュレーション波形の一部をそれぞれ示す。Fig. 2.15, 2.16, 2.17 より,本シミュレーション条件の電流制限値 5.0 A 近傍で,各セルの電流値が制限されていることが確認できる。第 2.2.1 節で述べたように,本論文では電流制限値  $i_{ref}$  によるオン/オフ制御を用いているために,オン/オフのタイミングによっては電流が  $i_{ref}$  を超える場合がある。そこで,本シミュレーションのパラメータ設計にあたっては, $i_{ref}$  の値をバッテリセルの定格電流値よりも十分に小さくするとともに, $i(T_{cnt})$  についても 1.56 A のような 5.0 A から大きなマージンをとった値を設定した。そのため,設計上は i が最大で 6.6 A 程度流れる可能性があるが,実際の電流波形を見ると最大で 5.6 A となっており,想定した 6.6 A 以内に収まっている。したがって,前節のように使用するバッテリセルの定格電流値に対して余裕を持たせたパラメータを選択することで,提案回路は目的の電流制御が可能であることが示された。

Fig. 2.15. Simulation current waveforms of each cell of three series-connected cells.

Fig. 2.16. Simulation current waveforms of each cell of eight series-connected cells.

Fig. 2.17. Simulation current waveforms of each cell of sixteen series-connected cells.

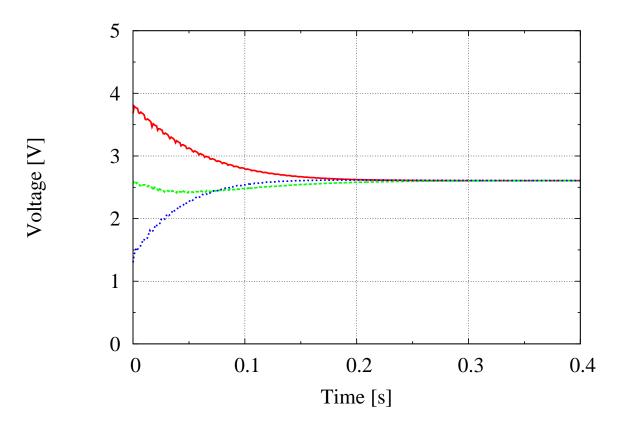

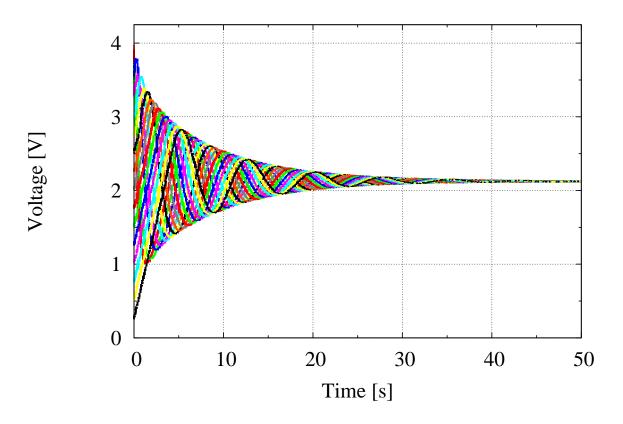

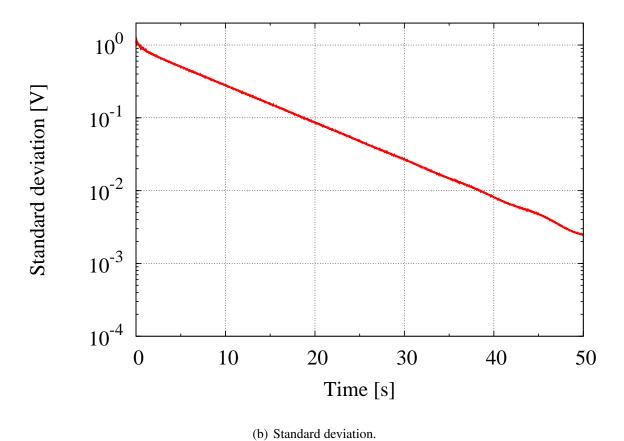

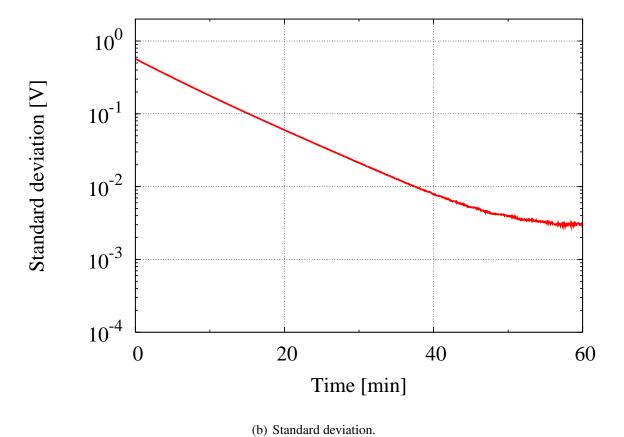

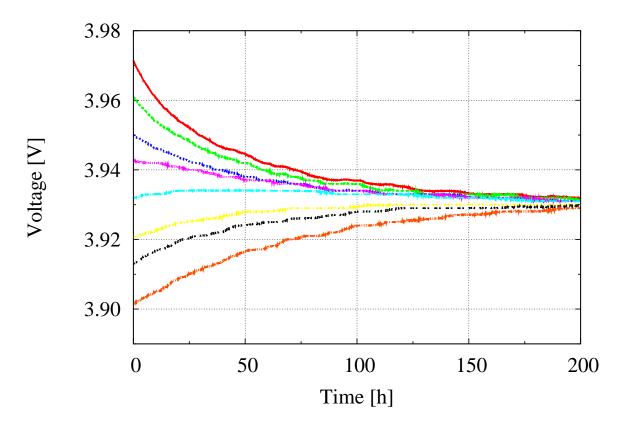

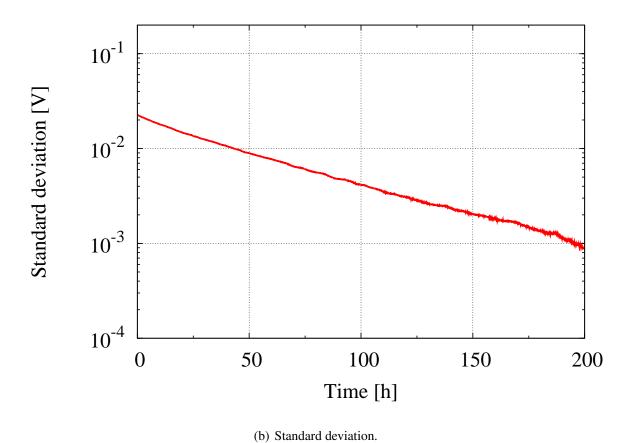

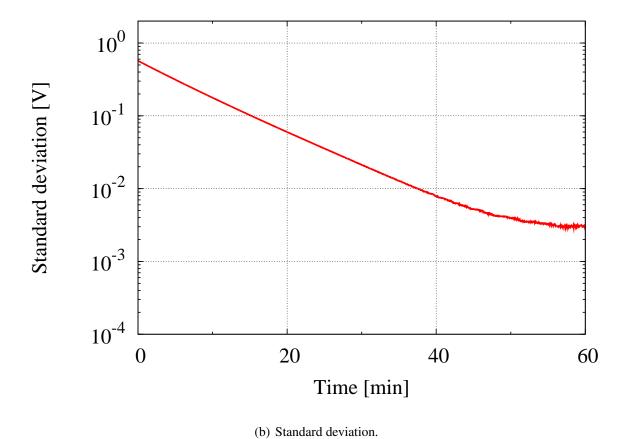

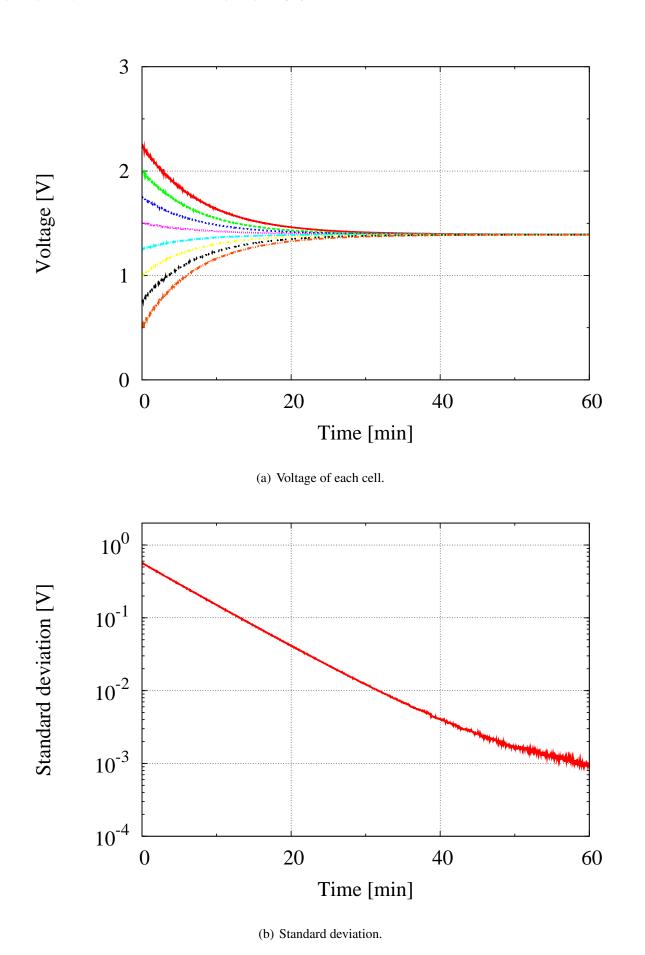

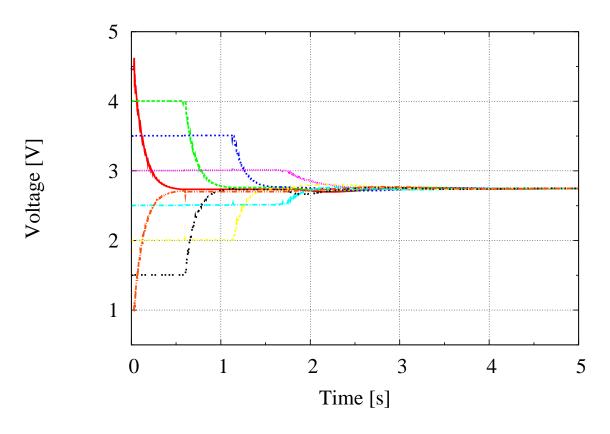

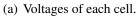

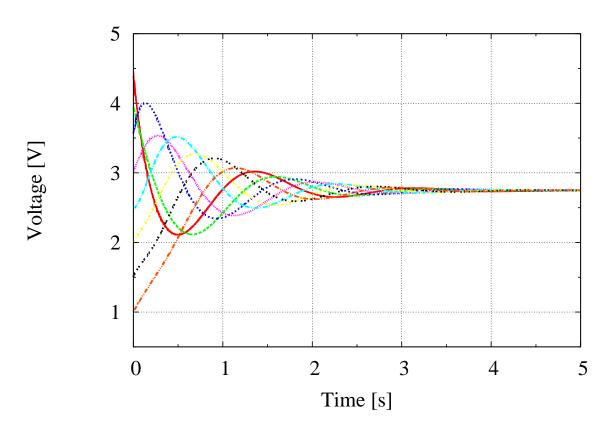

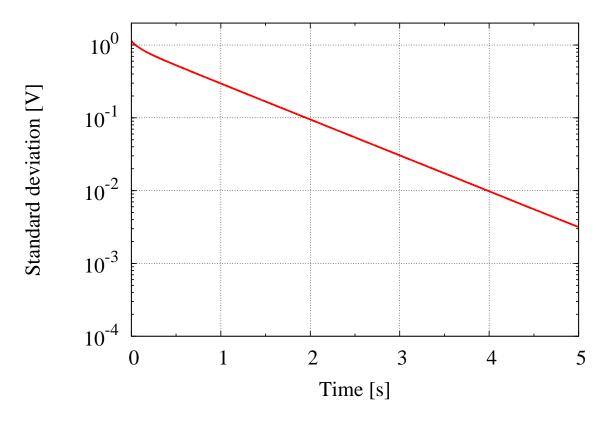

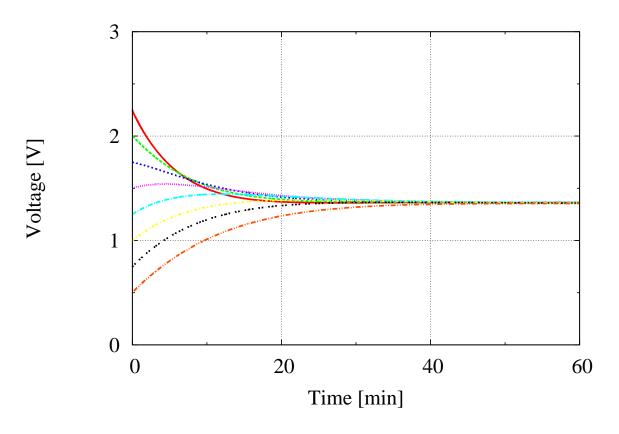

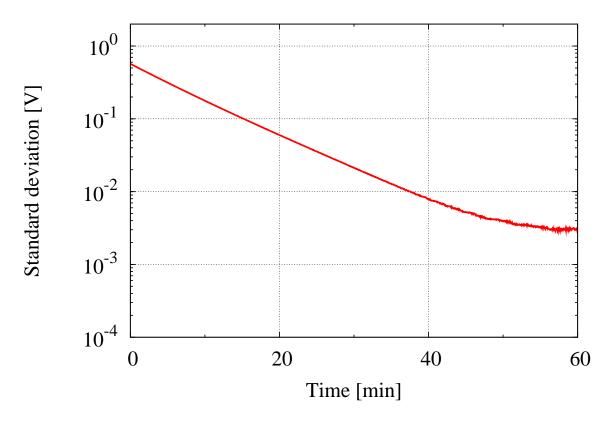

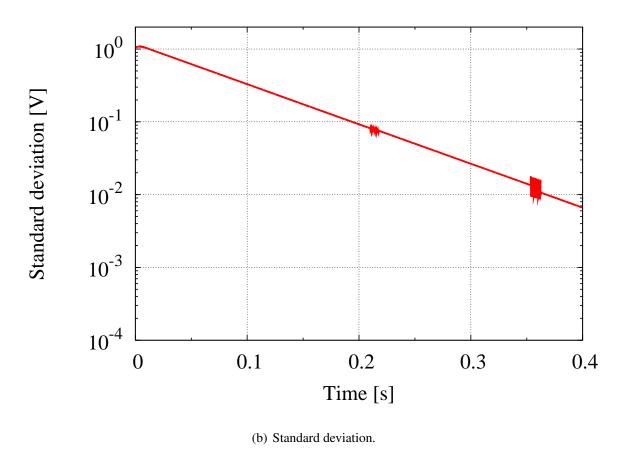

また、バッテリセルが3セル直列の場合について、セル電圧均等化動作時における各セル電圧、および電圧値の標準偏差のシミュレーション結果をFig. 2.18に示す。Fig. 2.18より、各セル電圧のばらつきは時間とともに解消されていることがわかる。一般的に、EDLCやリチウムイオンバッテリのセル電圧均等化動作では各セル電圧の標準偏差を10 mV 以下とすることが求められており[4]、シミュレーション結果は標準偏差が十分低い値まで低減されたことを示している。

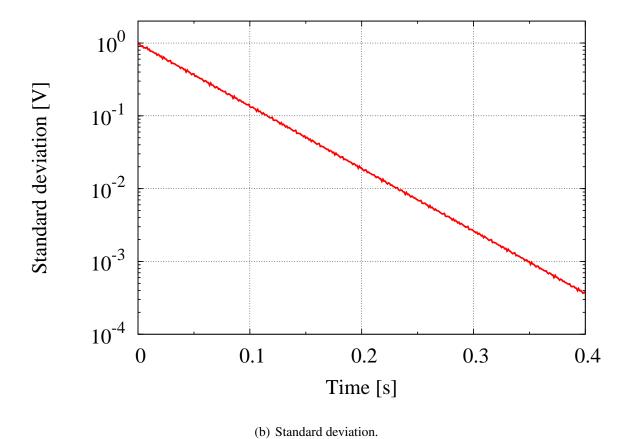

更に、バッテリセルが8セル直列の場合と16セル直列の場合についても同様に、セル電圧均等化動作時における各セル電圧、および電圧値の標準偏差のシミュレーション結果をFig. 2.19、2.20に示す。Fig. 2.19、2.20より、8セルおよび16セルの場合においても各セル電圧のばらつきは時間とともに解消され、標準偏差は最終的に10mV以下の十分低い値まで低減されたことがわかる。したがって、提案回路の有用性は示された。

ここで、セル数の違いによる動作特性への影響について考える。本節のシミュレーションにおいては、3 セル、8 セル、16 セルのそれぞれの場合において初期電圧の標準偏差がおおよそ等しくなるように初期条件を設定した。そのため、各セルの電圧を均等化するために移動すべき電荷量はセル数に比例して増加する。これにより、均等化時間についてもセル数の増加とともに増大することが示唆され、これはシミュレーション結果からも明らかである。一方、各セル電圧の時間的な推移や各セルに流れる電流の特性については、セル数に関係なくほぼ同様であることが確認された。したがって、セル数の違いによる提案回路の動作特性への影響としては、セル数の増加に伴って均等化時間が長くなる一方で、各セルの電圧や電流の時間的推移については影響が小さいことから、次章以降のシミュレーションおよび実機実験においては、主として8セルの場合についてのみ検証することとした。

Fig. 2.18. Simulation results of the proposed cell voltage equalizer connected to three series-connected cells.

Fig. 2.19. Simulation results of the proposed cell voltage equalizer connected to eight series-connected cells.

(b) Standard deviation.

Fig. 2.20. Simulation results of the proposed cell voltage equalizer connected to sixteen series-connected cells.

## 2.4 実機実験による動作特性の検証

提案回路の有用性およびシミュレーションの妥当性について検討するため,60FのEDLCセルをを3つ直列に接続した場合,8つ直列に接続した場合,および7.5 Ahのリチウムイオンバッテリセルを8つ直列に接続した場合における均等化動作の実機実験を行った。なお,前節のシミュレーションでは16セルについても検討したが,実機実験においては使用した測定機器の制約上,16セルでは十分なサンプリング速度でのセル電圧測定が行えないことから8セルまでの検証とした。

実機実験に用いた回路パラメータを Table 2.12, Table 2.13, および Table 2.14 に示す。回路 パラメータは使用する EDLC モジュールおよびリチウムイオンバッテリモジュールに合わせ, また, 実験装置の ESR 等を考慮して, 第 2.2 節に示した設計手順に基づき再考した。

なお、本論文では以降の実機実験にバッテリセルとして 60 Fの EDLC を用いた。これは、バッテリセルの入手性や実機実験の安全性、実験条件設定の容易さ等を考慮した結果である。そのため、実際に電気自動車用として使用されているリチウムイオンバッテリ等と比較すると充放電容量が小さく、以下の実験条件と同程度のセル電圧のばらつきを均等化する場合には均等化に長い時間を要すると考えられる。しかしながら、提案回路では均等化するバッテリモジュールに合わせてインダクタンス L やキャパシタンス C を設計する点や、実際の使用ではばらつきの小さい段階から均等化動作を行うことが可能であることから、提案回路は電気自動車用のリチウムイオンバッテリ等にも適用可能であると考えられる。以降ではこれを前提として、提案回路の有用性を検討することとした。

Table 2.12. Circuit parameters in the experiment for the three series-connected EDLC cells.

| Number of cells <i>n</i>           | 3                      |

|------------------------------------|------------------------|

| Battery module type                | EDLC                   |

| Battery cell capacity              | 60 F                   |

| ESR of each battery cell           | $32~\mathrm{m}\Omega$  |

| Initial voltage of $V_{\rm B1-B3}$ | 0.50-1.90 V            |

|                                    | (0.70 V step)          |

| ESR of inductor and capacitor $r$  | $349~\mathrm{m}\Omega$ |

| Inductance L                       | 199 μΗ                 |

| Capacitance C                      | 4734 μF                |

| Control frequency $f_{cnt}$        | 50 kHz                 |

| Cell change cycle $T_{\rm CC}$     | 1.60 ms                |

| Current limit value $i_{ref}$      | 2.0 A                  |

|                                    |                        |

Table 2.13. Circuit parameters in the experiment for the eight series-connected EDLC cells.

| Number of cells <i>n</i>           | 8                      |

|------------------------------------|------------------------|

| Battery module type                | EDLC                   |

| Battery cell capacity              | 60 F                   |

| ESR of each battery cell           | $32~\text{m}\Omega$    |

| Initial voltage of $V_{\rm B1-B8}$ | 0.50–2.25 V            |

|                                    | (0.25 V step)          |

| ESR of inductor and capacitor $r$  | $349~\mathrm{m}\Omega$ |

| Inductance L                       | $199  \mu \mathrm{H}$  |

| Capacitance C                      | $4734  \mu \mathrm{F}$ |

| Control frequency $f_{cnt}$        | 50 kHz                 |

| Cell change cycle $T_{\rm CC}$     | 1.60 ms                |

| ·                                  |                        |

| Current limit value $i_{\rm ref}$  | 2.0 A                  |

Table 2.14. Circuit parameters in the experiment for the eight series-connected lithium-ion battery cells.

| Number of cells <i>n</i>           | 8                   |

|------------------------------------|---------------------|

| Battery module type                | Lithium-ion battery |

| Battery cell capacity              | 7.5 Ah              |

| ESR of each battery cell           | 20 mΩ               |

| Initial voltage of $V_{\rm B1-B8}$ | 3.90–3.97 V         |

|                                    | (0.01 V step)       |

| ESR of inductor and capacitor r    | 132 mΩ              |

| Inductance L                       | 47 μΗ               |

| Capacitance C                      | 6312 μF             |

| Control frequency $f_{cnt}$        | 50 kHz              |

| Cell change cycle $T_{\rm CC}$     | 0.90 ms             |

| Current limit value $i_{ref}$      | 2.0 A               |

|                                    |                     |

EDLC セルを 3 つ直列に接続した場合のセル電圧均等化動作時における各セル電圧,および電圧値の標準偏差の実験結果を Fig. 2.21 に示す。Fig. 2.21 より,各セル電圧のばらつきは時間とともに解消され,標準偏差は最終的に 10 mV 以下の十分低い値まで低減されたことがわかる。

同様に、EDLCセルを8つ直列に接続した場合の均等化動作時における各セル電圧、および電圧値の標準偏差の実験結果をFig. 2.22に示す。Fig. 2.22より、各セル電圧のばらつきは時間とともに解消され、標準偏差は最終的に10mV以下の十分低い値まで低減されたことがわかる。

ここで、実験により得られた各モジュール電圧波形 Fig. 2.21(a), 2.22(a) とシミュレーションにより得られた各セル電圧波形 Fig. 2.18(a), 2.19(a) を比較すると、3 直列の場合、および8 直列の場合のどちらも各セル電圧や標準偏差の推移の挙動が一致していることがわかる。これにより、前述のシミュレーション結果は妥当であるといえる。

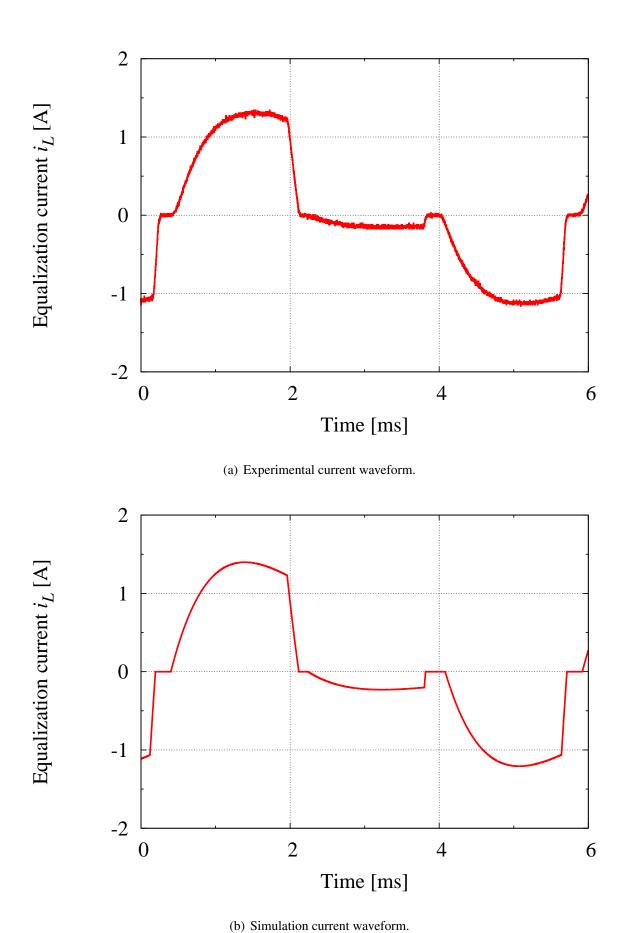

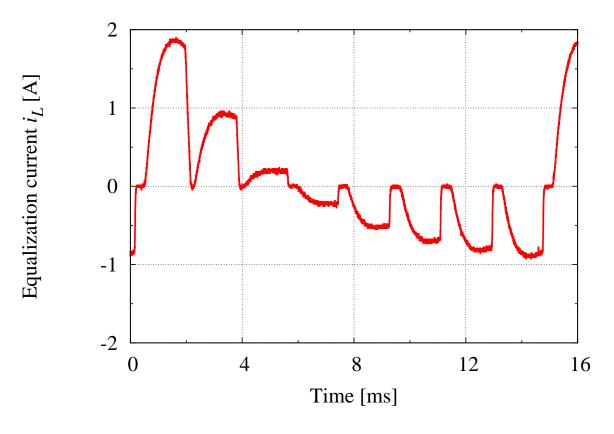

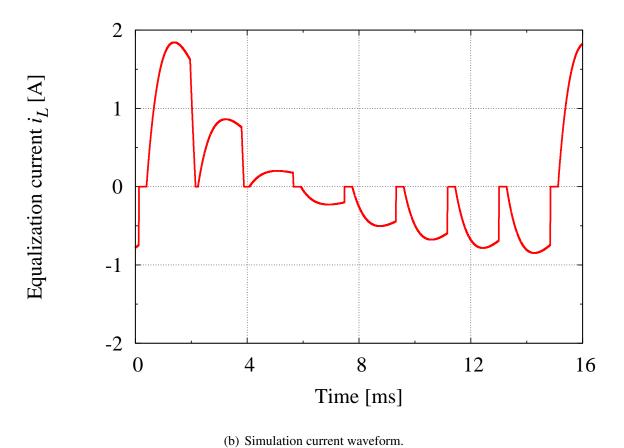

また、3 直列および8 直列の実験時における均等化電流  $i_L$  の波形を Fig. 2.23(a), 2.24(a), 実機実験と同条件の回路パラメータを用いたシミュレーションにおける均等化電流  $i_L$  の波形を Fig. 2.23(b), 2.24(b) にそれぞれ示す。まず、3 直列の場合について Fig. 2.23(a) および Fig. 2.23(b) を比較すると、均等化電流  $i_L$  の概形および挙動がよく似ていることがわかる。また、同様に 8 直列の場合についても Fig. 2.24(a) および Fig. 2.24(b) を比較すると、均等化電流  $i_L$  概形および挙動がよく似ていることがわかる。したがって、シミュレーションの妥当性は均等化電流  $i_L$  の波形からも確認された。

ここで、EDLC セルを 8 直列にした場合における均等化動作時の効率  $\eta_{LC}$  [%] について考える。なお、効率の計算にあたっては、均等化動作前に各 EDLC セルが有していた静電エネルギー  $U_{\mathrm{pre}}$  [J] と、各セル電圧の標準偏差が  $10\mathrm{mV}$  となったときの静電エネルギー  $U_{\mathrm{10mV}}$  [J] の関係から式 (2.12) を用いて求めることとした。

式 (2.12) より、8 直列の場合における均等化動作時の効率は、Table 2.13 の条件においては

$$\eta_{\rm LC} = \frac{U_{\rm 10mV}}{U_{\rm pre}} \times 100 \tag{2.12}$$

$$= 84.1 [\%]$$

(2.13)

と求まる。同様に、Table 2.13 の条件でパッシブ型 [12] を用いたときの効率損失  $\eta_R$  について考えると、全てのセルの電圧が  $V_{B8}$  となるように抵抗を用いて電力を消費させるので

$$\eta_{\rm R} = 11.3 \, [\%]$$

(2.14)

と求まる。したがって、提案回路ではパッシブ型と比較して均等化動作時の損失が小さく、Table 2.13 の条件においては均等化動作時の効率を約73 pt 向上可能なことが確認された。

また,提案回路とパッシブ型 [12] の均等化時間について考える。Fig. 2.22 より,Table 2.13 の条件における提案回路の均等化時間  $T_{\rm eqLC}$  は 37.2 min であった。同様に,Table 2.13 の条件でパッシブ型を用いた場合の均等化時間  $T_{\rm eqR}$  について考えると,最大入力電圧 2.25 V に対して最大電流を 2.0 A とすれば,パッシブ型で均等化動作に用いる抵抗値  $R_{\rm eq}$  は

$$R_{\text{eq}} = \frac{2.25 \,[\text{V}]}{2.0 \,[\text{A}]} = 1.13 \,[\Omega]$$

(2.15)

と求まる。したがって、Table 2.13 の条件におけるパッシブ型の均等化時間  $T_{\text{eqR}}$  は

60 [F] × 0.50 [V] = 60 [F] × 2.25 [V]

$$\varepsilon^{-\frac{1}{60 \text{ [F]} \times 1.13 \text{ } \Omega}}^{T_{\text{eqR}}}$$

$$\therefore T_{\text{eqR}} \cong 3.30 \text{ [min]}$$

(2.16)

と求まり、提案回路の均等化時間  $T_{\text{eqLC}}$  は、最大電流を同一条件とした場合のパッシブ型の均等化時間  $T_{\text{eqR}}$  と比較すると、10 倍程度長いことがわかる。

Fig. 2.21. Experimental results of the proposed cell voltage equalizer connected to three series-connected EDLC cells.

Fig. 2.22. Experimental results of the proposed cell voltage equalizer connected to eight series-connected EDLC cells.

Fig. 2.23. Comparison of the experimental and simulation current waveforms of each cell (n = 3).

(a) Experimental current waveform.

Fig. 2.24. Comparison of the experimental and simulation current waveforms of each cell (n = 8).

#### 第2章 LC直列回路方式セル電圧均等化回路の提案

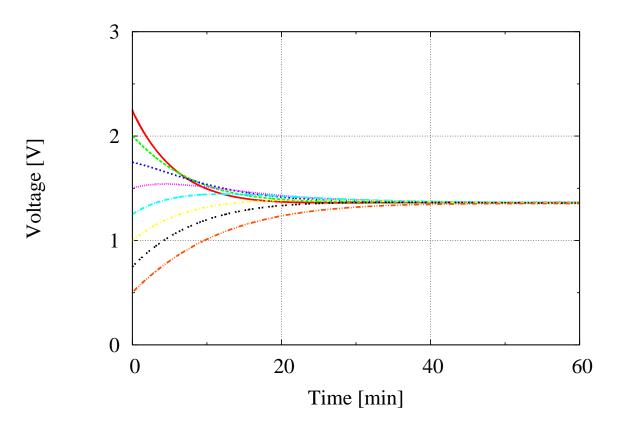

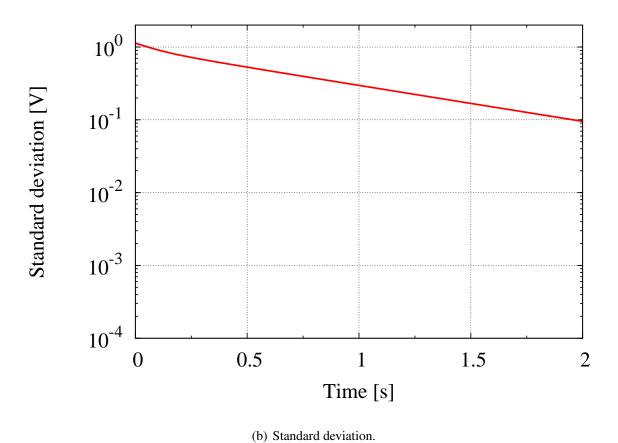

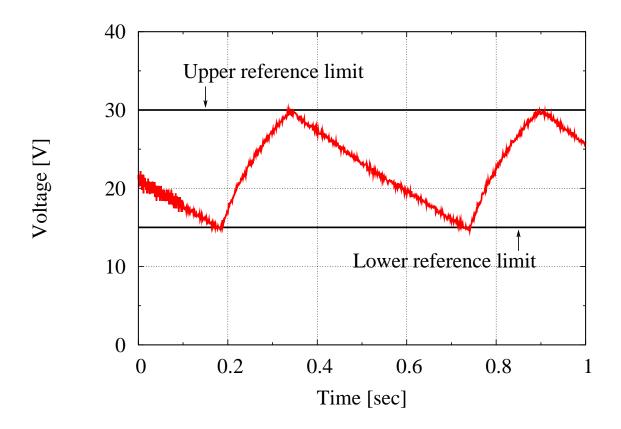

最後に、リチウムイオンバッテリセルを 8 つ直列に接続した場合の均等化動作時における各セル電圧、および電圧値の標準偏差の実験結果を Fig. 2.25 に示す。 Fig. 2.25 より、EDLCセルを用いた場合と同様に各セル電圧のばらつきは時間とともに解消され、標準偏差は最終的に10mV以下の十分低い値まで低減されたことがわかる。したがって、提案回路はリチウムイオンバッテリに対しても有用であることが示された。

なお、リチウムイオンバッテリの実機実験では、EDLCを用いた場合と比較して初期電圧のばらつきを小さく設定した。これは、リチウムイオンバッテリの特性上、使用可能電圧範囲がEDLCと比較して狭いためである。本実機実験の初期電圧条件は、リチウムイオンバッテリの実使用電圧範囲内となるような電圧値を選定し、実験を行った。また、Fig. 2.25(a) に着目すると、前述のEDLCを用いた実機実験では見られなかった、各セル電圧の脈動が確認できる。これは、リチウムイオンバッテリの実機実験がEDLCと比較して長い時間を要したために、昼夜の温度差に起因したバッテリモジュールや提案回路の微妙なパラメータ変化による影響が現れたものである。しかしながら、Fig. 2.25(b) に示した標準偏差の傾きには大きな変化が認められないことから、温度差による均等化動作への影響は微小であったと考えられる。

Fig. 2.25. Experimental results of the proposed cell voltage equalizer connected to eight series-connected lithium-ion battery cells.

## 2.5 提案回路の課題

前述のシミュレーションおよび実機実験では、Fig. 2.2 に示した Mode 1-n を順次繰り返すことでセル電圧の均等化を図っていた (以下,この制御法を従来制御法と呼ぶ)。このとき,均等化電流  $i_L$  は各バッテリ電圧  $V_{B1-Bn}$  および各回路パラメータ  $(r,L,C,T_{CC}$  など) により決定される。ここで,各回路パラメータは均等化動作中に変化しないと仮定すれば,均等化電流  $i_L$  は  $V_{B1-Bn}$  の初期値に依存すると考えられる。したがって, $V_{B1-Bn}$  の初期値によっては均等化電流  $i_L$  は小さくなり,これにより均等化時間が長くなる場合がある。

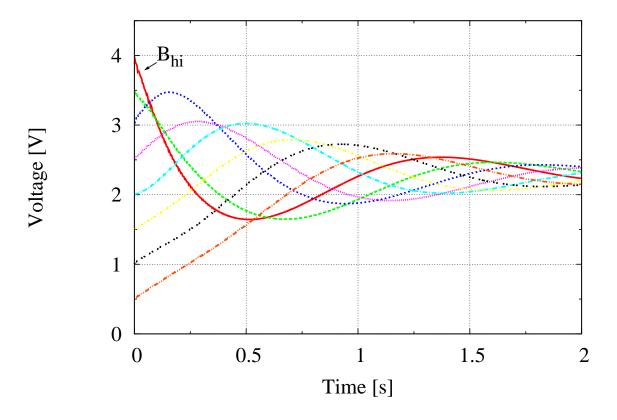

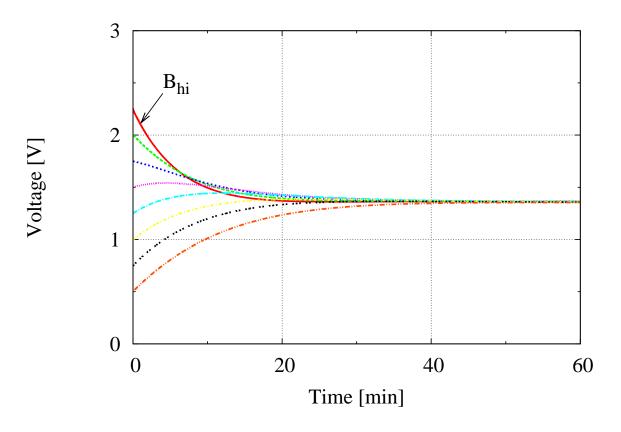

また、均等化動作の中で、均等化に直接関与しない充放電が生じる場合がある。Fig. 2.26に、2.3節における従来制御法を用いた 8 直列セルのシミュレーション結果の時間軸を拡大したものを示す。Fig. 2.26(a) に示す各セル電圧値波形のうち、初期電圧値が最も高いセル  $B_{hi}$  に着目すると、 $B_{hi}$  の電圧値  $V_{Bhi}$  は、最終的に収束する電圧値よりも一度低い電圧値をとってから収束するように推移していることがわかる。また、他セルの電圧値も同様な推移をしていることが読み取れる。これは、提案回路の均等化動作の特徴として、各 Mode により選択されたセルの電圧値は直前の Mode で選択されていたセルの電圧値に近づくように動作するため、各 Mode の選択が周期的に繰り返される従来制御法では、全てのセルの電圧値が上下を繰り返しながら収束していくという特性を有するためである。したがって、従来制御法ではこのような均等化に直接関与しない充放電が生じることが、均等化動作の効率低下の一因となると考えられる。

更に、提案回路では各セルの切替のために多数の双方向スイッチを必要することから、回路の構造上、それぞれのゲート駆動回路に絶縁電源が必要となり、ゲート駆動回路が肥大化する可能性がある。"Photo-MOS リレー"のようなスイッチング素子を使うことでこの問題を解決することは可能であるが、"Photo-MOS リレー"はスイッチング速度が1kHz程度と遅いことから、回路パラメータ設計やより高度な制御を行う上での制約となる。

Fig. 2.26. Simulation results with the conventional method.

## 2.6 第2章のまとめ

本章では、第1章にて示した従来回路の課題に対して、アクティブ方式の採用による蓄電エネルギーの有効活用と均等化電流の動的な制御性、ならびに磁性素子の削減による回路規模の低減に着目した新たなセル電圧均等化回路として、LC直列回路方式セル電圧均等化回路を提案した。また、シミュレーションおよび実機実験による動作特性の検証結果から、提案回路はセル電圧均等化回路として有用であることを示した。更に実機実験の結果から、提案回路は従来の抵抗消費型のセル電圧均等化回路と比較して、前述の実験条件下では均等化動作の効率を約73 pt 向上可能であることが示された。最後に、提案回路の更なる有用性向上を考える上での指針とするため、提案回路が抱える課題について整理した。

# 第3章 擬似乱数列を用いた均等化時間低 減法

第3章では、第2章にて示した提案回路の課題の1つである均等化時間に対して、擬似乱数列を利用してセルの切替順をランダムとすることで、センサ等を追加することなく、制御法の変更のみで均等化時間を低減可能な制御法(以下、疑似乱数法と呼ぶ)を提案する。また、疑似乱数法の動作原理について説明するとともに、シミュレーションおよび実機実験により疑似乱数法の有用性を検証する。更に、疑似乱数法による均等化時間の特性変化について、従来制御法との比較や生成される擬似乱数列の精度の観点から考察する。

## 3.1 提案制御手法の概要と目的

第2.5節で述べたように、各回路パラメータが同一である場合、提案回路の均等化時間は接続するバッテリセルの初期条件と各 Mode の選択順により影響を受ける。このとき、セル数がnである場合には(n-1)!通りの切替順が考えられるが、前述の理由により、均等化時間は(n-1)!通りでそれぞれ異なると考えられる。従来制御法では、(n-1)!通りの選択順のうちの1つのみ(第1セルから第nセルを順に選択するパターンのみ)を繰り返しながら均等化動作を行うため、接続するバッテリセルの初期条件により均等化時間が決定される。

本章では、前述の均等化時間に関する問題点の解決策として、各 Mode の選択順を擬似乱数列を用いてランダムに選択する手法 (疑似乱数法) を提案する。疑似乱数法では (n-1)! 通り存在する切替順がランダムに選択されるため、疑似乱数法を適用した場合の均等化時間は、ランダム性が十分に確保されている場合においては、(n-1)! 通りそれぞれの均等化時間の平均値に収束する [51]。これにより、接続するバッテリセルの初期条件の影響を軽減することが可能となり、平均的な均等化時間の低減が期待できる。なお、本章では疑似乱数法の擬似乱数列の生成方法として、生成の簡易性などを考慮し線形合同法を採用した。

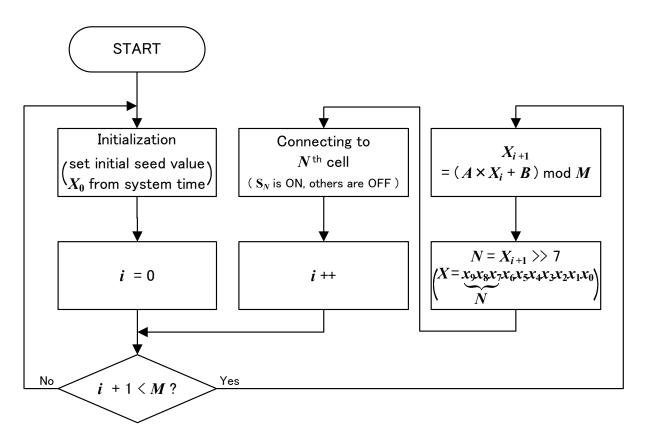

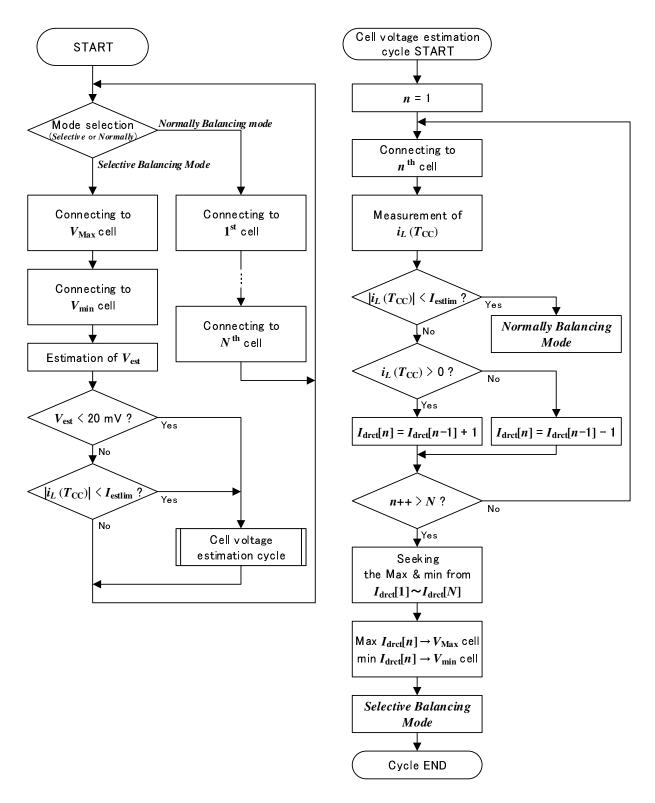

## 3.2 動作原理

Fig. 3.1 に疑似乱数法のフローチャートを示す。疑似乱数法では,線形合同法により 10 bit の 擬似乱数列 X ( $x_9x_8x_7x_6x_5x_4x_3x_2x_1x_0$ ) を生成し,その上位 3 bit を N ( $x_9x_8x_7$ ) として Mode の選択 (ON にするスイッチング素子  $S_N$  の選択) に用いる。これは,線形合同法の特徴として,下位 bit よりも上位 bit の方がよりランダム性が高いためである。ここで, $X_0$  は乱数の種であり,システム時刻により生成する 10 bit の自然数である。また,M は乱数の周期であり,本章では後述のシミュレーション,および実機実験におけるバッテリセル数 n=8 と比較して十分大きい 1024 (= 10 bit) に設定した。A,B はそれぞれ M>A>0,  $M>B\geq 0$  を満たす任意の定数であり(ただし, $X,i,n,M,A,B,N\in\mathbb{N}$ ),本章ではA=53,B=23 とした。以上のように設定することで,生成される擬似乱数列は周期 M で値を繰り返すが, $M\gg n$  であるため,各 Mode の選択はランダムであるとみなせ,M よりも十分に長い均等化時間中では各 Mode が選択される確率は一様となる。しかしながら,この手法では,最初に設定される  $X_0$  により M 内での各 Mode が選択される順序が一意に決まってしまう。そのため,本章では M 毎に新たな  $X_0$  を再度設定し,また, $X_0$  をシステム時刻より生成することで更にランダム性を向上させている。

疑似乱数法を適用することにより、従来制御法で周期的に選択されていた各 Mode がランダム性を持って選択される。各 Mode をランダムに選択することで、各セル電圧が最終的に収束する電圧値よりも一度低い電圧値をとってから収束するような推移を抑制し、均等化に直接関与しない不必要な充放電を低減する。これにより、疑似乱数法は従来制御法と比較して均等化時間を低減することが可能となる。

Fig. 3.1. Flowchart of the proposed equalization time reduction method using pseudo-random numbers.

## 3.3 シミュレーションによる有用性の検証

提案回路について、疑似乱数法の有用性について検討するため、EDLC セルの模擬としてキャパシタンス、および ESR を考慮したセルを 8 つ直列に接続した場合について、セル電圧均等化動作のシミュレーションを行った。本シミュレーションにおける回路パラメータを Table 3.1 に示す。また、本章では結果の一様性について検討するため、同様のシミュレーションを 20 回試行した。

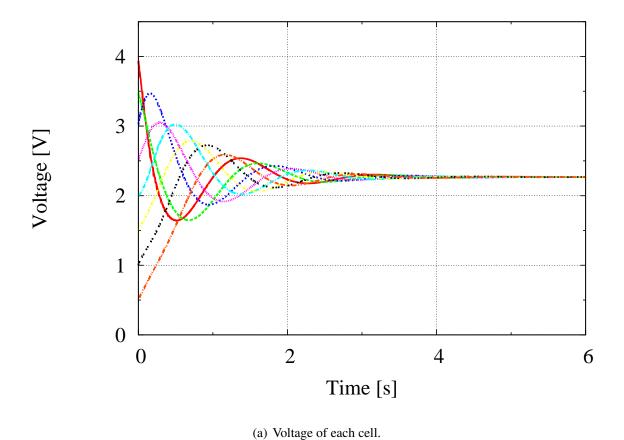

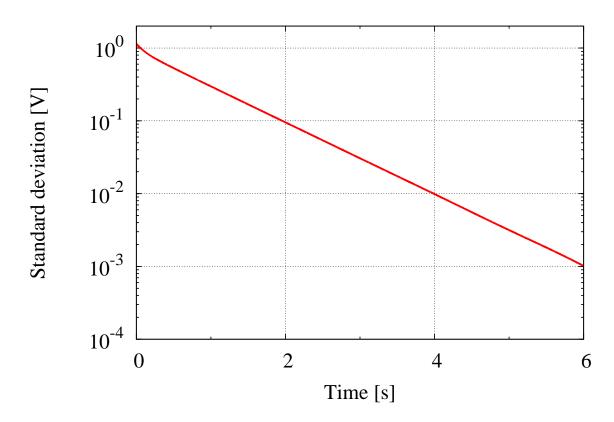

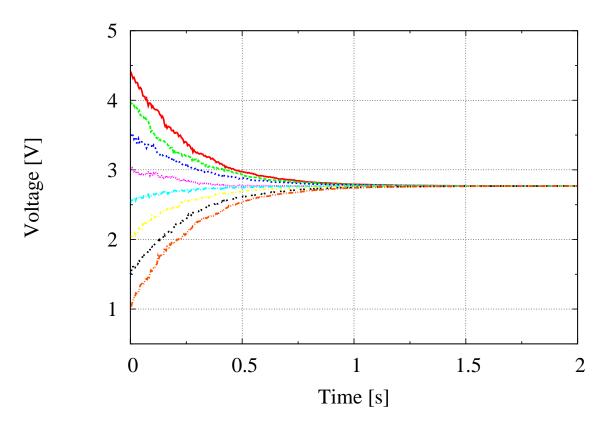

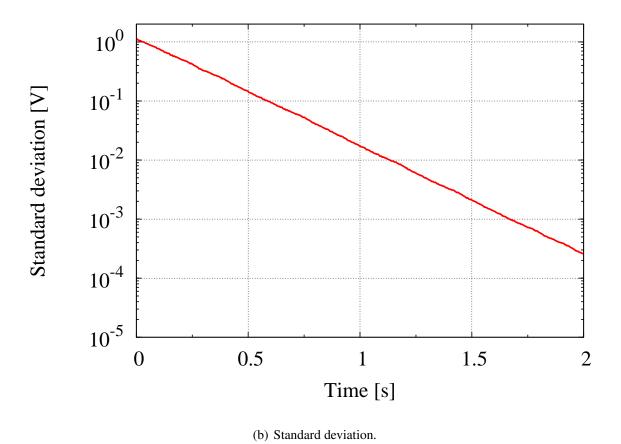

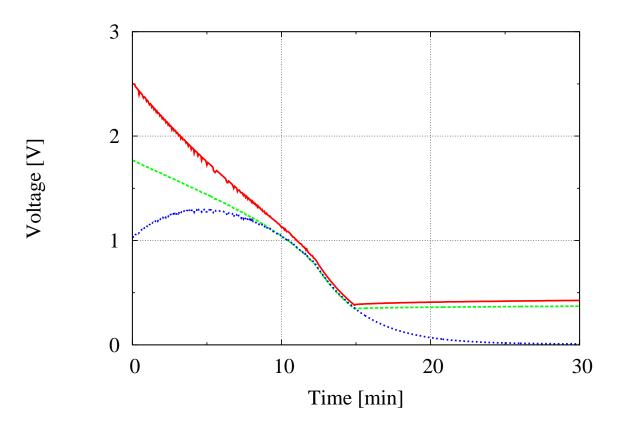

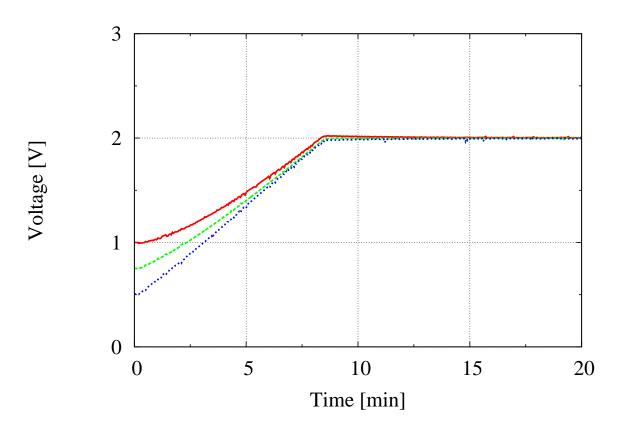

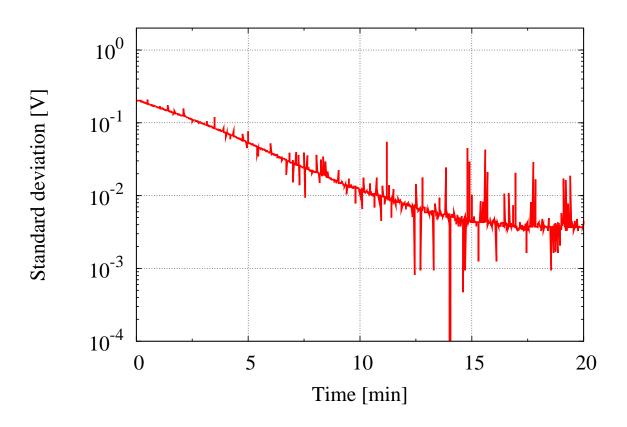

Fig. 3.2 に,ある均等化動作 1 試行 (各セルの初期電圧がそれぞれ  $V_{B1}$  = 4.50,  $V_{B2}$  = 4.00,  $V_{B3}$  = 3.50,  $V_{B4}$  = 3.00,  $V_{B5}$  = 2.50,  $V_{B6}$  = 2.00,  $V_{B7}$  = 1.50,  $V_{B8}$  = 1.00 のとき) における各セル電圧,および各セル電圧の標準偏差のシミュレーション結果を示す。Fig. 3.2(a) より,各セル電圧のばらつきは時間とともに解消されていることがわかる。また,Fig. 3.2(b) は各セル電圧の標準偏差を示しているが,一般的に EDLC 等のセル電圧均等化動作では各セル電圧の標準偏差を 10 mV以下とすることが求められており [4],シミュレーション結果は標準偏差が十分低い値まで低減されたことを示している。したがって,疑似乱数法においても,提案回路はセル電圧均等化動作が可能であることが示された。

Table 3.1. Circuit parameters in the simulation for the proposed reduction method using pseudorandom numbers.

| Number of cells <i>n</i>               | 8                      |

|----------------------------------------|------------------------|

| Battery cell capacity                  | 50 mF                  |

| ESR of each battery cell               | $100~\mathrm{m}\Omega$ |

| Initial voltage of $V_{\rm B1-B8}$     | 1.00–4.50 V            |

|                                        | (0.50 V step)          |

| ESR of inductor and capacitor <i>r</i> | 100 mΩ                 |

| Inductance L                           | $50  \mu \mathrm{H}$   |

| Capacitance C                          | $470\mu\mathrm{F}$     |

| Control frequency $f_{cnt}$            | 50 kHz                 |

| Cell change cycle $T_{\rm CC}$         | 0.24 ms                |

| Current limit value $i_{ref}$          | 5.0 A                  |

| Constant value A, B                    | 53, 23                 |

| Period of pseudo-random number M       | 10 bit                 |

|                                        |                        |

(a) Voltage of each cell.

Fig. 3.2. Simulation results with the proposed reduction method using pseudo-random numbers.

#### 3.3.1 従来制御法と疑似乱数法の比較

ここで、Fig. 3.3 に従来制御法によるシミュレーション結果を示す。回路パラメータは前述の Table 3.1 と同様とした。Fig. 3.2(a) と Fig. 3.3 を比較すると、疑似乱数法を用いることで、均等 化に直接関与しない充放電が抑制されていることがわかる。また、各セル電圧の標準偏差の傾きについても、疑似乱数法によるシミュレーション結果 (Fig. 3.2(b)) の方が従来制御法による シミュレーション結果 (Fig. 3.3(b)) と比較して傾きが急峻になっていることが確認できる。

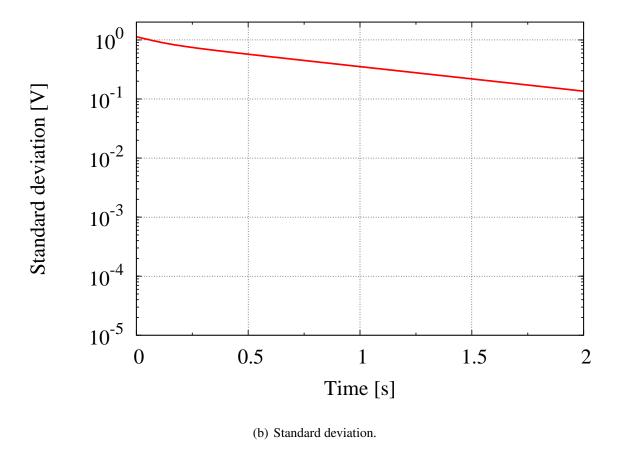

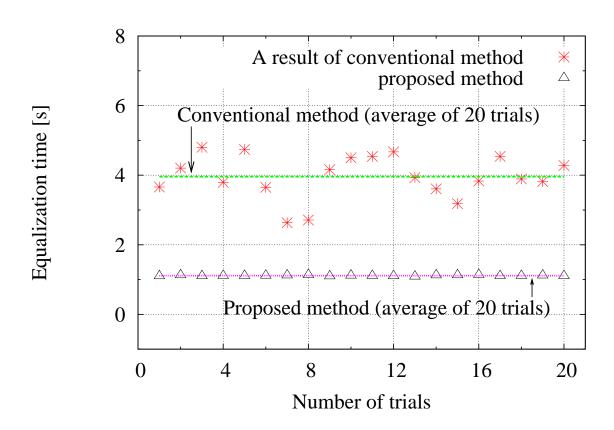

Fig. 3.4 に疑似乱数法と従来制御法について、それぞれ 20 回の試行における、各セル電圧の標準偏差が 10 mV となる時間 (均等化時間) のシミュレーション結果を示す。回路パラメータは、従来制御法と疑似乱数法とで同条件とし、初期電圧のばらつきはどちらも線形合同法により生成した擬似乱数列を用いて、1.00、1.50、2.00、2.50、3.00、3.50、4.00、4.50 V をランダムに設定した。Fig. 3.4 より、疑似乱数法と従来制御法のどちらにおいても、乱数を用いたことで各試行において均等化時間にばらつきが生じていることがわかる。しかしながら、疑似乱数法 20 回の平均均等化時間は約 1.11 s となっており、従来制御法 20 回での約 3.96 s の 28.1 % 程度となっている。したがって、疑似乱数法を用いることにより平均的な均等化時間を低減可能であることが明らかとなった。

(a) Voltage of each cell.

Fig. 3.3. Simulation results with conventional method (represented below as Fig. 2.26).

Fig. 3.4. Equalization time comparison between the proposed reduction method and the conventional method in the simulation.

## 3.4 実機実験による有用性の検証

提案回路について、疑似乱数法の有用性について検討するため、60 Fの EDLC モジュールを 8 つ直列に接続した場合について、セル電圧均等化動作の実機実験を行った。本実験で用いた 回路パラメータを Table 3.2 に示す。また、本節では結果の一様性について検討するため、同様 の実験を 10 回試行した。

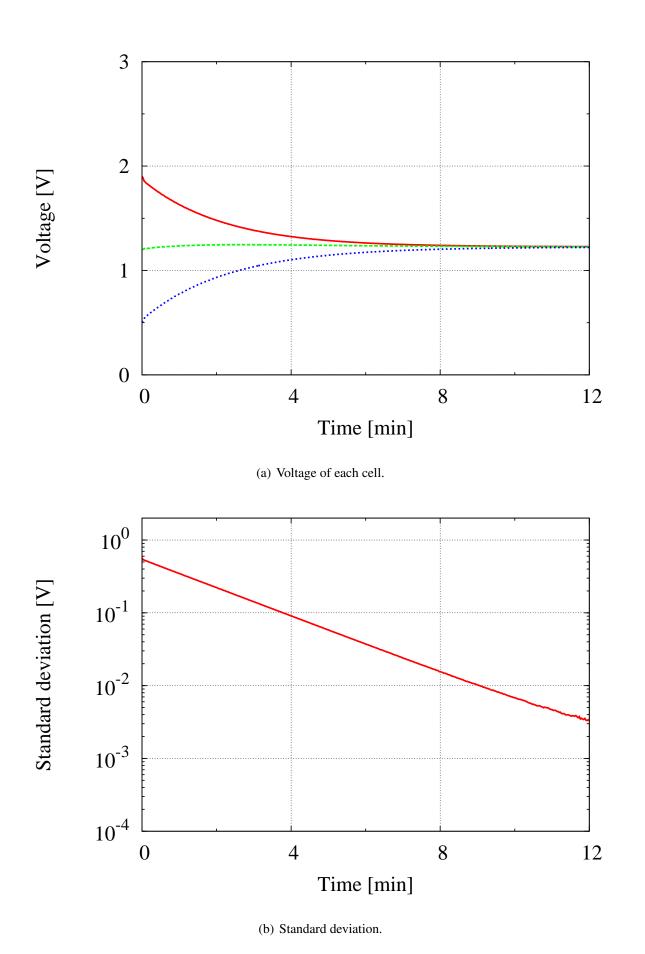

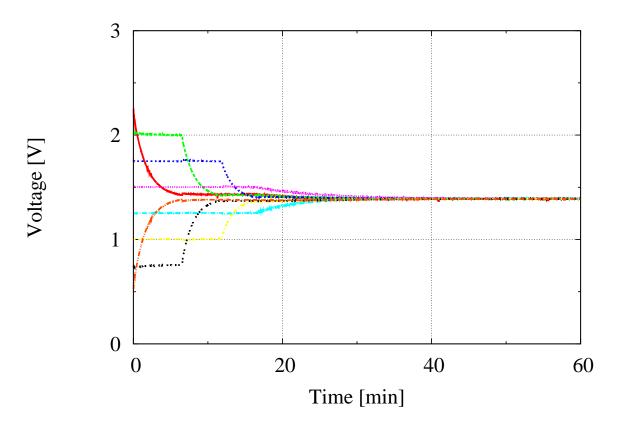

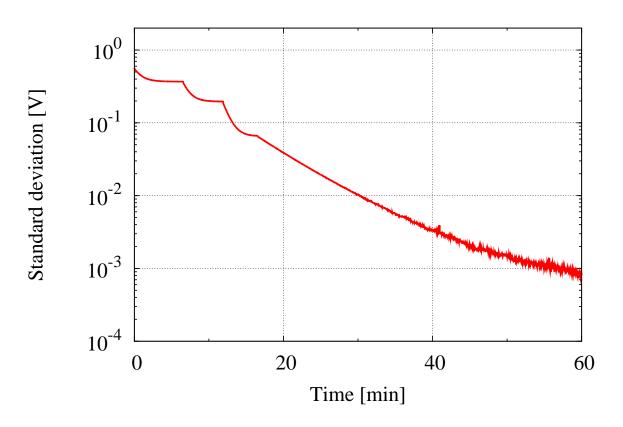

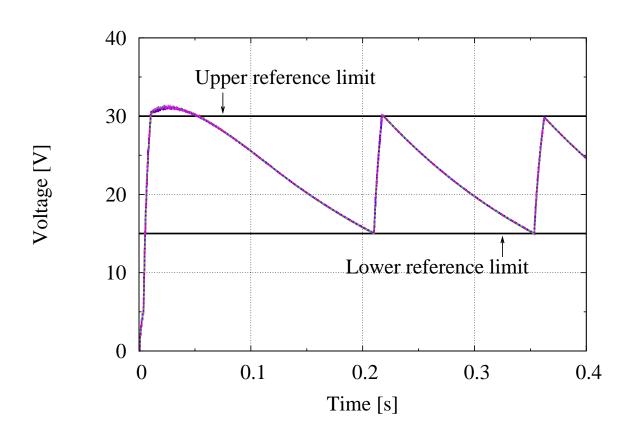

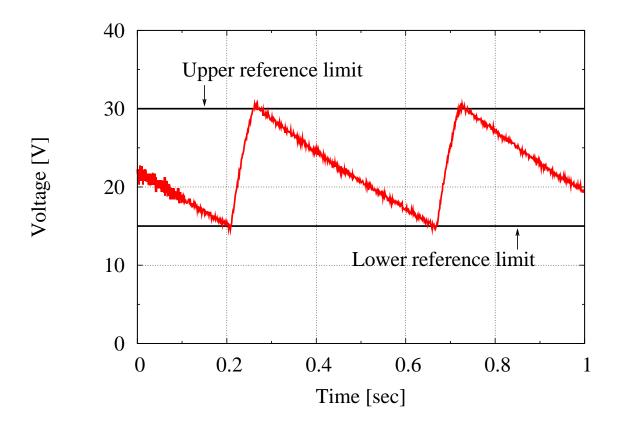

まず、従来制御法による実験結果を Fig. 3.5 に示す。回路パラメータは Table 3.2 を用いた。ここで、Fig. 3.5(a) に示す各セル電圧値波形の内、初期電圧値が最も高いセル  $B_{hi}$  に着目すると、従来制御法によるシミュレーション結果 (Fig. 2.26) と同様に、 $B_{hi}$  の電圧値  $V_{Bhi}$  は、最終的に収束する電圧値よりも一度低い電圧値をとってから収束するように推移していることがわかる。

Table 3.2. Circuit parameters in the experiment for the proposed reduction method using pseudorandom numbers.

| Number of cells <i>n</i>           | 8             |  |  |

|------------------------------------|---------------|--|--|

| Battery module type                | EDLC          |  |  |

| Battery cell capacity              | 60 F          |  |  |

| ESR of each battery cell           | 32 mΩ         |  |  |

| T '' 1 1 CT                        | 0.50–2.25 V   |  |  |

| Initial voltage of $V_{\rm B1-B8}$ | (0.25 V step) |  |  |

| ESR of inductor and capacitor r    | 349 mΩ        |  |  |

| Inductance L                       | 199 μΗ        |  |  |

| Capacitance C                      | 4734 μF       |  |  |

| Control frequency $f_{cnt}$        | 50 kHz        |  |  |

| Cell change cycle $T_{\rm CC}$     | 1.60 ms       |  |  |

| Current limit value $i_{ref}$      | 2.0 A         |  |  |

| Constant value A, B                | 53, 23        |  |  |

| Period of pseudo-random number M   | 10 bit        |  |  |

|                                    |               |  |  |

(a) Voltage of each cell.

Fig. 3.5. Experimental results with the conventional method.

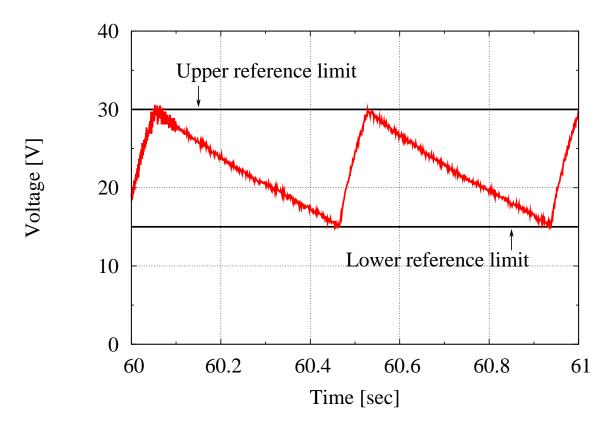

次に,疑似乱数法による,ある均等化動作 1 試行 (各セルの初期電圧がそれぞれ  $V_{B1}=2.25$ ,  $V_{B2}=2.00$ ,  $V_{B3}=1.75$ ,  $V_{B4}=1.50$ ,  $V_{B5}=1.25$ ,  $V_{B6}=1.00$ ,  $V_{B7}=0.75$ ,  $V_{B8}=0.50$  のとき) における各セル電圧,および各セル電圧の標準偏差の実験結果を Fig. 3.6 に示す。 Fig. 3.6(a) より,各セル電圧のばらつきは時間とともに解消されていることがわかる。また, Fig. 3.6(b) は各セル電圧の標準偏差を示しているが,最終的に  $10\,\mathrm{mV}\,\mathrm{U}$ 下まで低減されており,実験結果は標準偏差が十分低い値まで低減されたことを示している。したがって,実機実験においても,疑似乱数法はセル電圧均等化動作が可能であることが示された。

Fig. 3.6. Experimental results with the proposed reduction method using pseudo-random numbers.

#### 3.4.1 従来制御法と疑似乱数法の比較

疑似乱数法の各セル電圧の実験波形 (Fig. 3.6(a)) と従来制御法による各セル電圧の実験波形 (Fig. 3.5(a)) を比較すると、前述のシミュレーション結果と同様に、均等化に直接関与しない充放電が抑制されていることがわかる。また、各セル電圧の標準偏差の傾きについても、疑似乱数法による実験結果 (Fig. 3.6(b)) の方が従来制御法による実験結果 (Fig. 3.5(b)) と比較して傾きが急峻になっていることが確認できる。

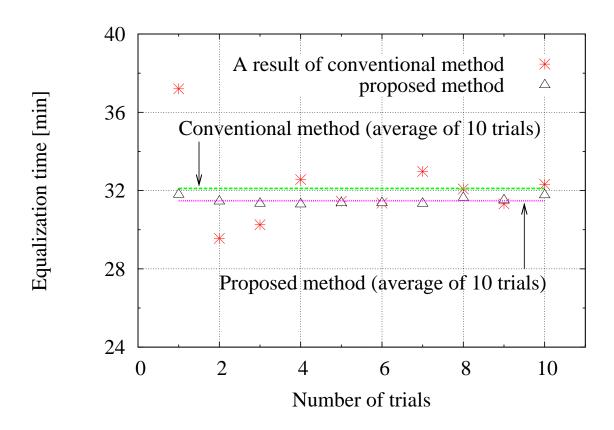

Fig. 3.7 に疑似乱数法と従来制御法について,それぞれ 10 回の試行における,各セル電圧の標準偏差が 10 mV となる時間 (均等化時間) の実験結果を示す。回路パラメータは,従来制御法と疑似乱数法とで同条件とし,初期電圧のばらつきはどちらも線形合同法により生成した擬似乱数列を用いて,0.50, 0.75, 1.00, 1.25, 1.50, 1.75, 2.00, 2.25 V をランダムに設定した。Fig. 3.7 より,疑似乱数法と従来制御法のどちらにおいても,乱数を用いたことで各試行において均等化時間にばらつきが生じていることがわかる。しかしながら,平均均等化時間は約 31.48 minとなっており,従来制御法10回での約 32.11 min の 98.0 %程度となっている。したがって,パラメータによる差異はあるものの,実機実験においても疑似乱数法を用いることにより平均的な均等化時間を低減可能であることが示された。

Fig. 3.7. Equalization time comparison between the proposed reduction method and the conventional method in the experiment.

## 3.5 平均均等化時間についての考察